# **IQS9320 DATASHEET**

Multi-Channel Inductive Sensing Device Aimed at Keyboard Applications

#### **1** Device Overview

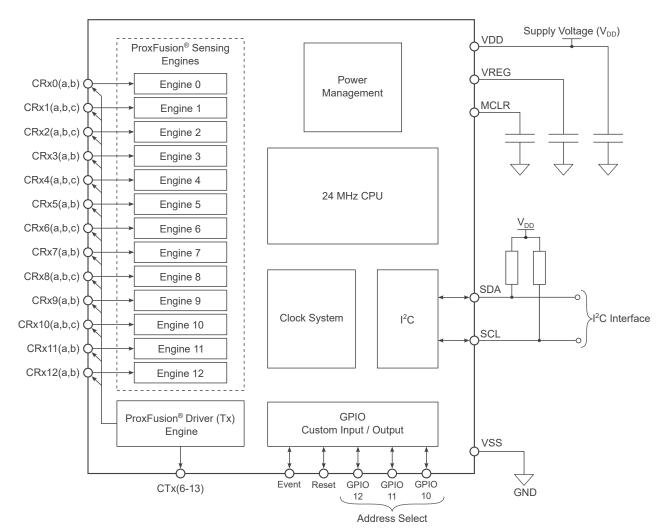

The IQS9320 ProxFusion<sup>®</sup> IC is a flexible multi-channel inductive sensing device that supports a high number of channels per device, adjustable actuation points, analogue data streaming, and high report rates. The TriggerMax<sup>™</sup> UI allows for dynamic actuation based on the distance a key is pressed or released. Other features include automatic tuning and long-term environmental tracking.

#### 1.1 Main Features

- > Up to 20 inductive sensors

- > Greater than 1 kHz sampling rate

- > Per key adjustable actuation points

- > Activation hysteresis

- > TriggerMax<sup>™</sup> dynamic actuation

- > Sensor flexibility:

- Automatic sensor tuning for optimal sensitivity

- Internal voltage regulator

- On-chip noise filtering

- > RF immunity

- I<sup>2</sup>C communication interface with IRQ/RDY, up to Fast-Mode Plus (1 MHz)

- > Selectable I<sup>2</sup>C addresses

- > Analogue channel data streaming

- > Multi-device GPIO interface

- > Multi-device synchronised sampling

- > Environmental tracking

- > QFN52  $(6 \times 6 \times 0.75 \text{ mm}) 0.4 \text{ mm}$  pitch

- > Wide input voltage supply range: 2.2 V to 3.5 V

- > Wide operating temperature range: -40 °C to +85 °C

## 1.2 Applications

- > Mechanical keyboards

- > Waterproof buttons

- > Remote controls

- > Gaming controllers

# 1.3 System Overview

Figure 1.1: IQS9320 Block Diagram

# Contents

| 1 | Device Overview11.1Main Features11.2Applications11.3System Overview2                                                                                                                                                                                                                                   |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | QFN52 Pinout       5         2.1       I <sup>2</sup> C Interface Configuration       5         2.2       GPIO Interface Configuration       7                                                                                                                                                         |

| 3 | Reference Schematic       9         3.1       I <sup>2</sup> C Interface Configuration       9         3.2       GPIO Interface Configuration       10                                                                                                                                                 |

| 4 | Electrical Characteristics114.1Absolute Maximum Ratings114.2General Operating Conditions114.3ESD Rating114.4Reset Levels114.5MCLR Pin Levels and Characteristics124.6Recommended Operating Conditions124.7I²C Characteristics134.8Current consumption14                                                |

| 5 | Application and Implementation       15         5.1       Sampling Rate       15         5.2       Multiple Devices       16         5.2.1       I <sup>2</sup> C Interface Configuration for Multiple Devices       16         5.2.2       GPIO Interface Configuration for Multiple Devices       16 |

| 6 | ProxFusion® Module206.1Counts216.2Automatic Tuning Implementation (ATI)216.3Reference Tracking (LTA)216.3.1Reference Halt216.3.2Fast Reference226.4Delta226.5Normalised Delta226.6Channel Activation226.7TriggerMax <sup>™</sup> 23                                                                    |

| 7 | GPIO Interface         24           7.1         Key Scan         24           7.2         I <sup>2</sup> C Configuration         25           7.3         Event/Standby Mode         26                                                                                                                |

| 8 | Power Modes278.1Mode Selection278.2Mode Parameters278.3Automatic Power Modes278.4Standby Mode27                                                                                                                                                                                                        |

| 9  | Addit<br>9.1<br>9.2<br>9.3<br>9.4                                           | Reset Indication                                                                                                                                                                                                                                                                                                                                                                                                              | 28<br>28<br>28<br>28<br>28<br>28<br>28                                                                                                                                                                                                                    |

|----|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 | <b>I<sup>2</sup>C In</b><br>10.1<br>10.2<br>10.3<br>10.4                    | Module Specification       2         I <sup>2</sup> C Address Options       2         Memory Management       2         Read and Write Operations       3         10.4.1       I <sup>2</sup> C Read From Specific Address       3         10.4.2       I <sup>2</sup> C Read From Default Address       3                                                                                                                    | <b>29</b><br>29<br>29<br>29<br>30<br>30<br>30                                                                                                                                                                                                             |

| 11 | <b>Order</b><br>11.1<br>11.2                                                | Ordering Code                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>32</b><br>32                                                                                                                                                                                                                                           |

| 12 | <b>QFN5</b><br>12.1<br>12.2<br>12.3                                         | QFN52 Package Outline    3      QFN52 Recommended Footprint    3                                                                                                                                                                                                                                                                                                                                                              | <b>33</b><br>33<br>34<br>35                                                                                                                                                                                                                               |

| 13 | I <sup>2</sup> C M                                                          | emory Map 3                                                                                                                                                                                                                                                                                                                                                                                                                   | 86                                                                                                                                                                                                                                                        |

| A  | Memo<br>A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>A.7<br>A.8<br>A.9<br>A.10 | System Status (0x1000)       33         ATI Error Flags (0x1002)       33         Reference Halt Flags (0x1006)       44         Activation Flags (0x100A)       44         System Control (0x2000)       44         System Configuration (0x2002)       44         Multiplier and Divider Selection (0x3000 - 0x3026)       44         Channel Disable (0x3106)       44         Timing Generator Settings (0x3146)       44 | <b>18</b><br>18<br>19<br>10<br>12<br>14<br>15<br>16<br>18<br>19<br>19<br>19<br>19<br>19<br>10<br>10<br>12<br>14<br>15<br>16<br>16<br>18<br>19<br>19<br>10<br>12<br>14<br>15<br>16<br>16<br>16<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19 |

| в  | <b>Code</b><br>B.1<br>B.2<br>B.3                                            | GPIO Sequence: Key Scan    5      GPIO Sequence: I <sup>2</sup> C Configuration    5                                                                                                                                                                                                                                                                                                                                          | 50<br>51<br>52                                                                                                                                                                                                                                            |

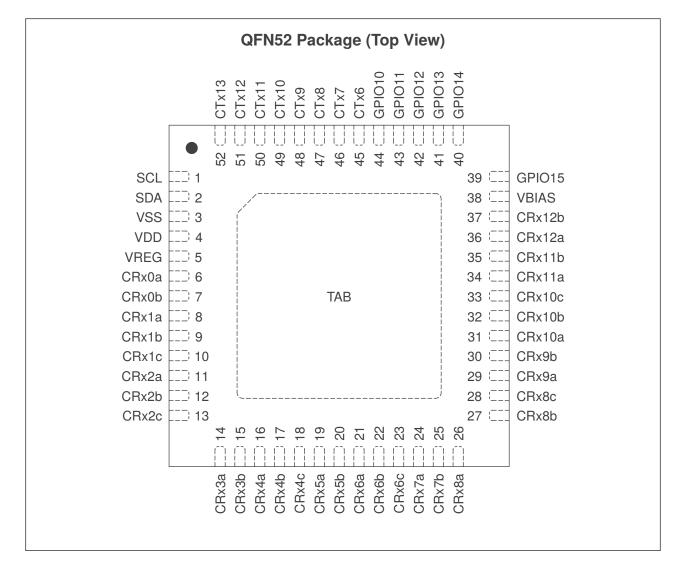

# 2 QFN52 Pinout

Figure 2.1: QFN52 Pinout

# 2.1 I<sup>2</sup>C Interface Configuration

| Pin | Name  | Type <sup>(i)</sup> | Function                | Description                             |  |

|-----|-------|---------------------|-------------------------|-----------------------------------------|--|

| 1   | SCL   | I/O                 | l <sup>2</sup> C        | I <sup>2</sup> C data                   |  |

| 2   | SDA   | I/O                 | l <sup>2</sup> C        | I <sup>2</sup> C I <sup>2</sup> C clock |  |

| 3   | VSS   | Р                   | Power                   | ower Analog/digital ground              |  |

| 4   | VDD   | Р                   | Power                   | Power supply input voltage              |  |

| 5   | VREG  | Р                   | Power                   | Internally-regulated supply voltage     |  |

| 6   | CRx0a | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                         |  |

| 7   | CRx0b | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                         |  |

| 8   | CRx1a | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                         |  |

#### Table 2.1: QFN52 Pin Descriptions

Continued on next page ...

#### Table 2.1: QFN52 Pin Descriptions (Continued)

| Pin | Name   | Type <sup>(i)</sup> | Function                | Description                       |

|-----|--------|---------------------|-------------------------|-----------------------------------|

| 9   | CRx1b  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 10  | CRx1c  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 11  | CRx2a  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 12  | CRx2b  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 13  | CRx2c  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 14  | CRx3a  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 15  | CRx3b  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 16  | CRx4a  | I/O                 | ProxFusion®             | Inductive RX/TX                   |

| 17  | CRx4b  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 18  | CRx4c  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 19  | CRx5a  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 20  | CRx5b  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 21  | CRx6a  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 22  | CRx6b  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 23  | CRx6c  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 24  | CRx7a  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 25  | CRx7b  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 26  | CRx8a  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 27  | CRx8b  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 28  | CRx8c  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 29  | CRx9a  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 30  | CRx9b  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 31  | CRx10a | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 32  | CRx10b | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 33  | CRx10c | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 34  | CRx11a | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 35  | CRx11b | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 36  | CRx12a | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 37  | CRx12b | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                   |

| 38  | VBIAS  | _                   | ProxFusion <sup>®</sup> | _                                 |

| 39  | GPIO15 | I                   | GPIO                    | MCLR                              |

| 40  | GPIO14 | 0                   | GPIO                    | Event Pin                         |

| 41  | GPIO13 | 0                   | GPIO                    | Reset Pin                         |

| 42  | GPIO12 | I                   | GPIO                    | I <sup>2</sup> C Address Select 0 |

| 43  | GPIO11 | I                   | GPIO                    | I <sup>2</sup> C Address Select 1 |

| 44  | GPIO10 | I                   | GPIO                    | I <sup>2</sup> C Address Select 2 |

| 45  | CTx6   | 0                   | ProxFusion <sup>®</sup> | Inductive TX                      |

Continued on next page...

| Pin | Name  | Type <sup>(i)</sup> | Function                | Description                              |

|-----|-------|---------------------|-------------------------|------------------------------------------|

| 46  | CTx7  | 0                   | ProxFusion <sup>®</sup> | Inductive TX                             |

| 47  | CTx8  | 0                   | ProxFusion <sup>®</sup> | Inductive TX                             |

| 48  | CTx9  | 0                   | ProxFusion <sup>®</sup> | Inductive TX                             |

| 49  | CTx10 | 0                   | ProxFusion <sup>®</sup> | Inductive TX                             |

| 50  | CTx11 | 0                   | ProxFusion <sup>®</sup> | Inductive TX                             |

| 51  | CTx12 | 0                   | ProxFusion <sup>®</sup> | Inductive TX/ External POSC Clock Output |

| 52  | CTx13 | I/O                 | ProxFusion <sup>®</sup> | Inductive TX/ External POSC Clock Input  |

#### Table 2.1: QFN52 Pin Descriptions (Continued)

<sup>i</sup> Pin Types: I = Input, O = Output, I/O = Input or Output, P = Power

# 2.2 GPIO Interface Configuration

#### Type<sup>(i)</sup> Pin Name Function Description I<sup>2</sup>C I<sup>2</sup>C data 1 SCL I/O I<sup>2</sup>C I<sup>2</sup>C clock 2 SDA I/O 3 VSS Ρ Analog/digital ground Power 4 Ρ VDD Power Power supply input voltage 5 VREG Ρ Power Internally-regulated supply voltage 6 I/O ProxFusion<sup>®</sup> Inductive RX/TX CRx0a 7 CRx0b I/O ProxFusion<sup>®</sup> Inductive RX/TX ProxFusion<sup>®</sup> 8 CRx1a I/O Inductive RX/TX ProxFusion<sup>®</sup> 9 CRx1b I/OInductive RX/TX **ProxFusion**<sup>®</sup> 10 CRx1c I/O Inductive RX/TX I/O ProxFusion<sup>®</sup> Inductive RX/TX 11 CRx2a 12 CRx2b I/O ProxFusion<sup>®</sup> Inductive RX/TX ProxFusion<sup>®</sup> CRx2c I/O Inductive RX/TX 13 14 CRx3a I/O ProxFusion<sup>®</sup> Inductive RX/TX ProxFusion<sup>®</sup> 15 CRx3b I/O Inductive RX/TX I/O ProxFusion<sup>®</sup> Inductive RX/TX 16 CRx4a **ProxFusion**<sup>®</sup> 17 CRx4b I/O Inductive RX/TX ProxFusion<sup>®</sup> CRx4c I/O Inductive RX/TX 18 19 CRx5a I/O ProxFusion<sup>®</sup> Inductive RX/TX ProxFusion<sup>®</sup> 20 CRx5b I/O Inductive RX/TX ProxFusion<sup>®</sup> 21 CRx6a I/O Inductive RX/TX I/O ProxFusion<sup>®</sup> Inductive RX/TX 22 CRx6b 23 I/O ProxFusion<sup>®</sup> Inductive RX/TX CRx6c I/O **ProxFusion**<sup>®</sup> 24 CRx7a Inductive RX/TX

#### Table 2.2: QFN52 Pin Descriptions

Continued on next page ...

#### Table 2.2: QFN52 Pin Descriptions (Continued)

| Pin | Name   | Type <sup>(i)</sup> | Function                | Description                              |

|-----|--------|---------------------|-------------------------|------------------------------------------|

| 25  | CRx7b  | I/O                 | ProxFusion®             | Inductive RX/TX                          |

| 26  | CRx8a  | I/O                 | ProxFusion®             | Inductive RX/TX                          |

| 27  | CRx8b  | I/O                 | ProxFusion®             | Inductive RX/TX                          |

| 28  | CRx8c  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                          |

| 29  | CRx9a  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                          |

| 30  | CRx9b  | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                          |

| 31  | CRx10a | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                          |

| 32  | CRx10b | I/O                 | ProxFusion®             | Inductive RX/TX                          |

| 33  | CRx10c | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                          |

| 34  | CRx11a | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                          |

| 35  | CRx11b | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                          |

| 36  | CRx12a | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                          |

| 37  | CRx12b | I/O                 | ProxFusion <sup>®</sup> | Inductive RX/TX                          |

| 38  | VBIAS  | _                   | ProxFusion <sup>®</sup> | -                                        |

| 39  | GPIO15 | I                   | GPIO                    | MCLR                                     |

| 40  | GPIO14 | I/O                 | GPIO                    | CO                                       |

| 41  | GPIO13 | I/O                 | GPIO                    | R0                                       |

| 42  | GPIO12 | 0                   | GPIO                    | R1                                       |

| 43  | GPIO11 | 0                   | GPIO                    | R2                                       |

| 44  | GPIO10 | I/O                 | GPIO                    | R3                                       |

| 45  | CTx6   | 0                   | ProxFusion <sup>®</sup> | Inductive TX                             |

| 46  | CTx7   | 0                   | ProxFusion <sup>®</sup> | Inductive TX                             |

| 47  | CTx8   | 0                   | ProxFusion <sup>®</sup> | Inductive TX                             |

| 48  | CTx9   | 0                   | ProxFusion <sup>®</sup> | Inductive TX                             |

| 49  | CTx10  | 0                   | ProxFusion®             | Inductive TX                             |

| 50  | CTx11  | 0                   | ProxFusion <sup>®</sup> | Inductive TX                             |

| 51  | CTx12  | 0                   | ProxFusion <sup>®</sup> | Inductive TX/ External POSC Clock Output |

| 52  | CTx13  | I/O                 | ProxFusion <sup>®</sup> | Inductive TX/ External POSC Clock Input  |

<sup>i</sup> Pin Types: I = Input, O = Output, I/O = Input or Output, P = Power

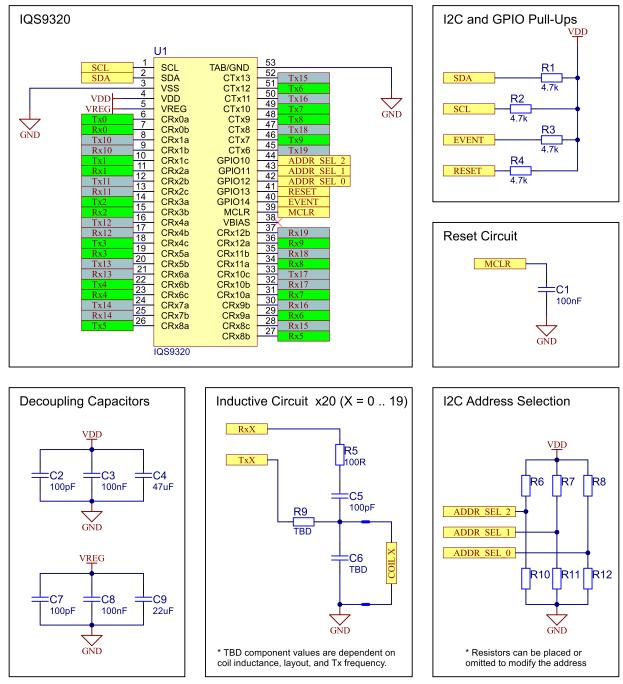

# 3 Reference Schematic

# 3.1 I<sup>2</sup>C Interface Configuration

\* Schematic subject to change without notice

Figure 3.1: IQS9320 Reference Schematic for I<sup>2</sup>C Interface

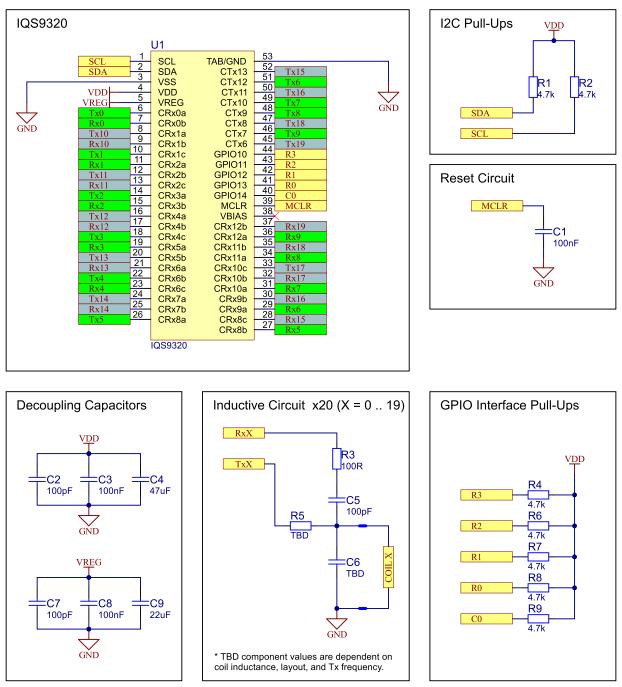

# 3.2 GPIO Interface Configuration

\* Schematic subject to change without notice

Figure 3.2: IQS9320 Reference Schematic for GPIO Interface

# 4 Electrical Characteristics

## 4.1 Absolute Maximum Ratings

#### Table 4.1: Absolute Maximum Ratings

| Symbol           | Rating                                                                 | Min  | Мах                                  | Unit |

|------------------|------------------------------------------------------------------------|------|--------------------------------------|------|

| V <sub>DD</sub>  | Voltage applied at VDD pin<br>(referenced to VSS)                      | -0.3 | 3.5                                  | V    |

| M                | Voltage applied to any ProxFusion <sup>®</sup> pin (referenced to VSS) | -0.3 | V <sub>REG</sub>                     | V    |

| V <sub>IN</sub>  | Voltage applied to any other pin (referenced to VSS)                   | -0.3 | V <sub>DD</sub> + 0.3<br>(3.5 V max) | V    |

| T <sub>stg</sub> | Storage temperature                                                    | -40  | 85                                   | °C   |

## 4.2 General Operating Conditions

#### Table 4.2: General Operating Conditions

| Symbol            | Parameter                                      | Тур  | Unit |

|-------------------|------------------------------------------------|------|------|

| F <sub>OSC</sub>  | Master clock frequency                         | 24   | MHz  |

| F <sub>POSC</sub> | ProxFusion <sup>®</sup> engine clock frequency | 16   | MHz  |

| V <sub>REG</sub>  | Internally-regulated supply output             | 1.80 | V    |

## 4.3 ESD Rating

#### Table 4.3: ESD Rating

|                    |                                 |                                                                      | Value | Unit |

|--------------------|---------------------------------|----------------------------------------------------------------------|-------|------|

| $V_{(\text{ESD})}$ | Electrostatic discharge voltage | Human-body model (HBM),<br>per ANSI/ESDA/JEDEC JS-001 <sup>(i)</sup> | ±2000 | V    |

<sup>i</sup> JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±2000 V may actually have higher performance.

#### 4.4 Reset Levels

#### Table 4.4: Reset Levels

| Parar | neter                                         | Min | Тур | Мах  | Unit |

|-------|-----------------------------------------------|-----|-----|------|------|

| VDD   | Power-up (Reset trigger) - slope > 100 V/s    |     |     | 1.65 | V    |

| VDD   | Power-down (Reset trigger) - slope < -100 V/s | 0.9 |     |      | V    |

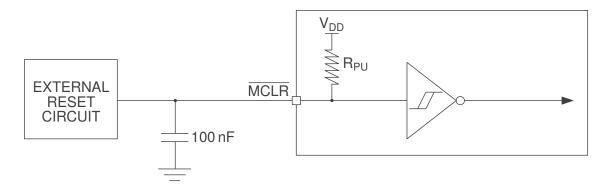

# 4.5 MCLR Pin Levels and Characteristics

#### Table 4.5: MCLR Pin Characteristics

| Para              | meter                                   | Min                         | Тур | Мах                         | Unit |

|-------------------|-----------------------------------------|-----------------------------|-----|-----------------------------|------|

| $V_{IL}$          | MCLR input low level voltage            | V <sub>SS</sub> – 0.3       |     | $0.25 \times V_{\text{DD}}$ | V    |

| VIH               | MCLR input high level voltage           | $0.75 \times V_{\text{DD}}$ |     | $V_{DD} + 0.3$              | V    |

| R <sub>PU</sub>   | MCLR pull-up equivalent resistor        |                             | 210 |                             | kΩ   |

| t <sub>Trig</sub> | MCLR input pulse width - ensure trigger | 250                         |     |                             | ns   |

Figure 4.1: MCLR Pin Diagram

# 4.6 Recommended Operating Conditions

#### Table 4.6: Recommended Operating Conditions

| Symbol            | Parameter                                                                 | Min               | Recommended         | Мах | Unit |

|-------------------|---------------------------------------------------------------------------|-------------------|---------------------|-----|------|

| V <sub>DD</sub>   | Standard operating voltage, applied at VDD pin                            | 2.2               |                     | 3.5 | V    |

| T <sub>A</sub>    | Operating free-air temperature                                            | -20               |                     | 85  | °C   |

| C <sub>VDD</sub>  | Recommended capacitor at VDD                                              | C <sub>VREG</sub> | $2 \times C_{VREG}$ |     | μF   |

| C <sub>VREG</sub> | Recommended external buffer capacitor at VREG (ESR $\leq$ 200 m $\Omega)$ | 10 <sup>(i)</sup> | 22                  | 88  | μF   |

<sup>i</sup> Absolute minimum allowed capacitance value is 4.7 µF, after derating for voltage, temperature, and worst-case tolerance.

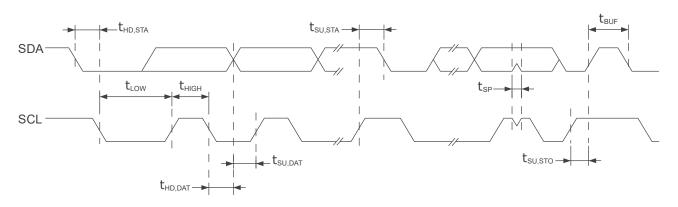

# 4.7 I<sup>2</sup>C Characteristics

#### Table 4.7: I<sup>2</sup>C Characteristics

| Parame              | ter                                                 | Min  | Мах  | Unit |

|---------------------|-----------------------------------------------------|------|------|------|

| f <sub>SCL</sub>    | SCL clock frequency                                 |      | 1000 | kHz  |

| t <sub>HD,STA</sub> | Hold time (repeated) START condition                | 0.26 |      | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                         | 0.5  |      | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                        | 0.26 |      | μs   |

| t <sub>SU,STA</sub> | Set-up time for a repeated START condition          | 0.26 |      | μs   |

| t <sub>HD,DAT</sub> | Data hold time                                      | 0    |      | ns   |

| t <sub>SU,DAT</sub> | Data set-up time                                    | 50   |      | ns   |

| t <sub>SU,STO</sub> | Set-up time for STOP condition                      | 0.26 |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition    | 0.5  |      | μs   |

| t <sub>SP</sub>     | Pulse duration of spikes suppressed by input filter | 0    | 50   | ns   |

## 4.8 Current consumption

The current draw of the IQS9320 is defined by the selected communication method, the number of channels being sampled, the number of raw counts sampled, and the sample rate of the active power mode. Table 4.8 indicates the mean current consumption for a given number of channels over a range of raw count values. All current measurements were taken at a Tx frequency of 16MHz and a conversion frequency of 8MHz with no I<sup>2</sup>C communication occurring between devices. The sample interval value may be written to the *Normal Power Sample Interval* register to achieve similar results.

| Mode                       | Number of<br>Channels | Sample Interval<br>[ms] | Current<br>Consumption<br>(Counts = 383)<br>[µA] | Current<br>Consumption<br>(Counts = 1023)<br>[μΑ] |

|----------------------------|-----------------------|-------------------------|--------------------------------------------------|---------------------------------------------------|

| I <sup>2</sup> C Interface | 20                    | 0                       | 7140                                             | 9540                                              |

| I <sup>2</sup> C Interface | 20                    | 5                       | 1680                                             | 1850                                              |

| I <sup>2</sup> C Interface | 20                    | 20                      | 570                                              | 615                                               |

| I <sup>2</sup> C Interface | 20                    | 50                      | 235                                              | 255                                               |

| I <sup>2</sup> C Interface | 20                    | 100                     | 125                                              | 130                                               |

| I <sup>2</sup> C Interface | 4                     | 0                       | 6180                                             | 6833                                              |

| I <sup>2</sup> C Interface | 4                     | 5                       | 1290                                             | 1400                                              |

| I <sup>2</sup> C Interface | 4                     | 20                      | 490                                              | 520                                               |

| I <sup>2</sup> C Interface | 4                     | 50                      | 205                                              | 215                                               |

| I <sup>2</sup> C Interface | 4                     | 100                     | 100                                              | 110                                               |

| GPIO Interface             | 20                    | 0                       | 7090                                             | 9470                                              |

| GPIO Interface             | 20                    | 5                       | 2390                                             | 2700                                              |

| GPIO Interface             | 20                    | 20                      | 1600                                             | 1690                                              |

| GPIO Interface             | 20                    | 50                      | 1440                                             | 1470                                              |

| GPIO Interface             | 20                    | 100                     | 1380                                             | 1390                                              |

| GPIO Interface             | 4                     | 0                       | 6110                                             | 6770                                              |

| GPIO Interface             | 4                     | 5                       | 1630                                             | 1740                                              |

| GPIO Interface             | 4                     | 20                      | 1280                                             | 1300                                              |

| GPIO Interface             | 4                     | 50                      | 1200                                             | 1210                                              |

| GPIO Interface             | 4                     | 100                     | 1180                                             | 1185                                              |

| Standby                    | -                     | -                       | 3                                                | 3                                                 |

#### Table 4.8: Current Consumption

# 5 Application and Implementation

# 5.1 Sampling Rate

The maximum sampling rate of the IQS9320 is defined by the number of channels sampled, the value of the raw counts sampled, and the active communication method. Table 5.1 provides the minimum and maximum sampling times for a given number of channels, and the mean sample times when each sample is read over the I<sup>2</sup>C or GPIO interface. The additional time required to respond to I<sup>2</sup>C communications is independent of the number of bytes transmitted. The additional time required for GPIO communications is defined by the number of channels the device is configured for.

| Number of<br>Channels | Minimum<br>Sample Time<br>(No Comms)<br>[μs] | Maximum<br>Sample Time<br>(No Comms)<br>[µs] | Mean<br>Sample Time<br>(I <sup>2</sup> C)<br>[µs] | Mean<br>Sample Rate<br>(I <sup>2</sup> C)<br>[kHz] | Mean<br>Sample Time<br>(GPIO)<br>[µs] | Mean<br>Sample Rate<br>(GPIO)<br>[kHz] |

|-----------------------|----------------------------------------------|----------------------------------------------|---------------------------------------------------|----------------------------------------------------|---------------------------------------|----------------------------------------|

| 20                    | 790                                          | 800                                          | 845                                               | 1.18                                               | 935                                   | 1.16                                   |

| 16                    | 650                                          | 670                                          | 710                                               | 1.41                                               | 760                                   | 1.32                                   |

| 12                    | 490                                          | 530                                          | 560                                               | 1.78                                               | 610                                   | 1.63                                   |

| 8                     | 350                                          | 420                                          | 435                                               | 2.30                                               | 445                                   | 2.25                                   |

| 4                     | 230                                          | 310                                          | 320                                               | 3.13                                               | 330                                   | 3.03                                   |

#### Table 5.1: Sampling Rate for Streaming

# 5.2 Multiple Devices

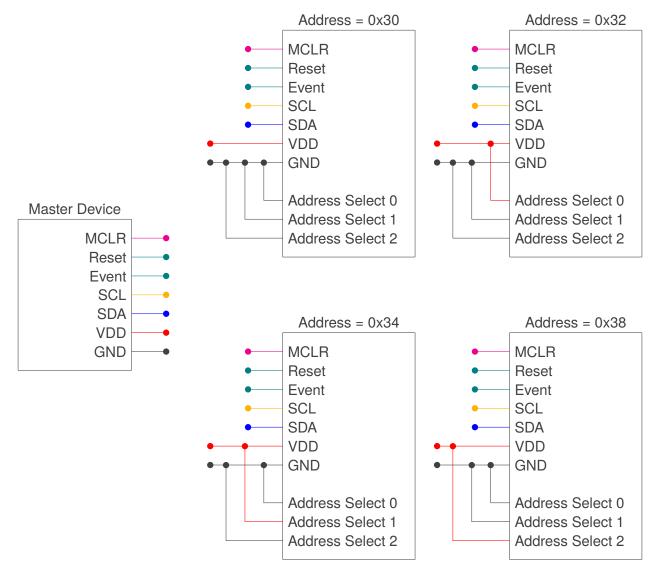

#### 5.2.1 I<sup>2</sup>C Interface Configuration for Multiple Devices

Multiple IQS9320 devices can be connected to a single  $I^2C$  bus by selecting the  $I^2C$  device address of each device with the state of the address select pins. The master device can sample all devices by sequentially addressing each device. The IQS9320 can be polled over  $I^2C$  at any time.

Figure 5.1 shows an example configuration with four IQS9320 devices, each configured to use a different I<sup>2</sup>C address using the address select pins.

Figure 5.1: Multiple Devices with  $l^2C$  Interface

The maximum sampling rate of a keyboard application is defined by the number of channels that are sampled by a single IQS9320 device. The number of channels per device defines the number of bytes that must be communicated over  $I^2C$  per device to complete a sample. The time required to read a given number of bytes from a default read address (section 10.4.2) over an  $I^2C$  connection with a clock speed of 1MHz is estimated as :

Time per Device

$$= 20\mu s + Bytes \times 10\mu s$$

(1)

The time required to complete  $I^2C$  communication per device determines the number of devices that can be sampled over a single  $I^2C$  bus for a given sampling rate. A maximum of 8 IQS9320 devices can be connected to a single  $I^2C$  peripheral.

| Number<br>of Keys | Sample Type      | Sample<br>Rate<br>[kHz] | Channels<br>per<br>Device | Bytes<br>per<br>Device | Time per<br>Device<br>[µs] | Number<br>of<br>Devices | Devices<br>per l <sup>2</sup> C<br>Periph-<br>eral | Number<br>of I <sup>2</sup> C<br>Periph-<br>erals |

|-------------------|------------------|-------------------------|---------------------------|------------------------|----------------------------|-------------------------|----------------------------------------------------|---------------------------------------------------|

| 104               | Activation Flags | 1                       | 20                        | 3                      | 50                         | 6                       | 8                                                  | 1                                                 |

| 104               | Activation Flags | 2                       | 10                        | 2                      | 40                         | 11                      | 8                                                  | 2                                                 |

| 104               | Activation Flags | 3                       | 4                         | 1                      | 30                         | 26                      | 8                                                  | 4                                                 |

| 87                | Activation Flags | 1                       | 20                        | 3                      | 50                         | 5                       | 8                                                  | 1                                                 |

| 87                | Activation Flags | 2                       | 10                        | 2                      | 40                         | 9                       | 8                                                  | 2                                                 |

| 87                | Activation Flags | 3                       | 4                         | 1                      | 30                         | 22                      | 8                                                  | 3                                                 |

| 68                | Activation Flags | 1                       | 20                        | 3                      | 50                         | 4                       | 8                                                  | 1                                                 |

| 68                | Activation Flags | 2                       | 10                        | 2                      | 40                         | 7                       | 8                                                  | 1                                                 |

| 68                | Activation Flags | 3                       | 4                         | 1                      | 30                         | 17                      | 8                                                  | 3                                                 |

| 104               | Normalised Delta | 1                       | 20                        | 20                     | 220                        | 6                       | 4                                                  | 2                                                 |

| 104               | Normalised Delta | 2                       | 10                        | 10                     | 120                        | 11                      | 4                                                  | 3                                                 |

| 104               | Normalised Delta | 3                       | 4                         | 4                      | 60                         | 26                      | 5                                                  | 6                                                 |

| 87                | Normalised Delta | 1                       | 20                        | 20                     | 220                        | 5                       | 4                                                  | 2                                                 |

| 87                | Normalised Delta | 2                       | 10                        | 10                     | 120                        | 9                       | 4                                                  | 3                                                 |

| 87                | Normalised Delta | 3                       | 4                         | 4                      | 60                         | 22                      | 5                                                  | 5                                                 |

| 68                | Normalised Delta | 1                       | 20                        | 20                     | 220                        | 4                       | 4                                                  | 1                                                 |

| 68                | Normalised Delta | 2                       | 10                        | 10                     | 120                        | 7                       | 4                                                  | 2                                                 |

| 68                | Normalised Delta | 3                       | 4                         | 4                      | 60                         | 17                      | 5                                                  | 4                                                 |

#### Table 5.2: I<sup>2</sup>C Application Requirements

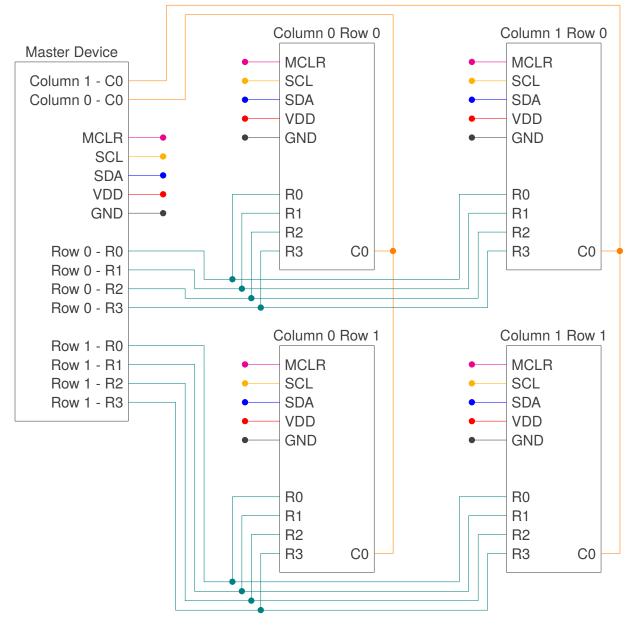

#### 5.2.2 GPIO Interface Configuration for Multiple Devices

Multiple IQS9320 devices can be placed in a matrix where the channel states of all devices in a column can be sampled simultaneously. The master device will sequentially query each column and read the response of all devices in the column from the state of the row output pins.

Figure 5.2 shows an example layout with four IQS9320 devices arranged in a  $2 \times 2$  device matrix.

All devices within the matrix share a single  $I^2C$  bus and have the same  $I^2C$  device address.  $I^2C$  communication can be enabled separately for each individual device by selecting a device using the row and column inputs.

Figure 5.2: Multiple Devices with GPIO Interface

The maximum sampling rate of a keyboard application that uses the GPIO interface as the communication method to devices in a matrix is defined by the number of channels sampled per device. The time required to sample a single column is also defined by the number of channels sampled per device. The time required to sample a single column can be used to calculate the number of columns that can be sampled during a given sampling period.

$$Maximum \ Columns = Floor(\frac{Sample \ Time}{Sample \ Time \ per \ Column})$$

(2)

The number of rows and columns can be selected such that the desired number of devices can be connected on the matrix and the number of columns does not exceed the limit calculated in Equation 2. The minimum number of GPIO pins required by the master device will be achieved by selecting a maximum number of columns and reducing the number of rows.

Number of

$$Devices = Columns \times Rows$$

(3)

$$GPIO Pins Required = Columns + 4 \times Rows$$

(4)

Table 5.3 provides a summary of possible device matrix layouts that can be applied to popular keyboard layouts.

| Number<br>of Keys | Sample Rate<br>[kHz] | Channels<br>per<br>Device | Time per<br>Column<br>[μs] | Maximum<br>Columns | Number<br>of<br>Devices | Columns | Rows | GPIO<br>Pins<br>Required |

|-------------------|----------------------|---------------------------|----------------------------|--------------------|-------------------------|---------|------|--------------------------|

| 104               | 1                    | 20                        | 140                        | 7                  | 6                       | 6       | 1    | 10                       |

| 104               | 2                    | 10                        | 100                        | 4                  | 11                      | 4       | 3    | 16                       |

| 104               | 3                    | 4                         | 60                         | 5                  | 26                      | 5       | 6    | 29                       |

| 87                | 1                    | 20                        | 140                        | 7                  | 5                       | 5       | 1    | 9                        |

| 87                | 2                    | 10                        | 100                        | 4                  | 9                       | 3       | 3    | 15                       |

| 87                | 3                    | 4                         | 60                         | 5                  | 22                      | 5       | 5    | 25                       |

| 68                | 1                    | 20                        | 140                        | 7                  | 4                       | 4       | 1    | 8                        |

| 68                | 2                    | 10                        | 100                        | 4                  | 7                       | 4       | 2    | 12                       |

| 68                | 3                    | 4                         | 60                         | 5                  | 17                      | 5       | 4    | 21                       |

#### Table 5.3: Key Scan Application Requirements

## 6 **ProxFusion<sup>®</sup> Module**

The IQS9320 ProxFusion<sup>®</sup> sensing architecture allows for up to 13 simultaneous inductive measurements with a total of up to 20 inductive channels that are sampled over 2 sampling cycles. The number of channels is defined by the sum of channels configured in the *Cycle 0 Channel Selection* and *Cycle 1 Channel Selection* registers.

The IQS9320 supports adjustable Rx and Tx pin selection for each channel. Table 6.1 lists the available Rx and Tx pin options with the associated value that must be written to the Rx Pin Selection and Tx Pin Selection registers.

| Value | Pin Description | Selection | Value | Pin Description | Selection |

|-------|-----------------|-----------|-------|-----------------|-----------|

| 0     | CRx0A           | Rx / Tx   | 23    | CRx9A           | Rx / Tx   |

| 1     | CRx0B           | Rx / Tx   | 24    | CRx9B           | Rx / Tx   |

| 2     | CRx1A           | Rx / Tx   | 25    | CRx10A          | Rx / Tx   |

| 3     | CRx1B           | Rx / Tx   | 26    | CRx10B          | Rx / Tx   |

| 4     | CRx1C           | Rx / Tx   | 27    | CRx10C          | Rx / Tx   |

| 5     | CRx2A           | Rx / Tx   | 28    | CRx11A          | Rx / Tx   |

| 6     | CRx2B           | Rx / Tx   | 29    | CRx11B          | Rx / Tx   |

| 7     | CRx2C           | Rx / Tx   | 30    | CRx12A          | Rx / Tx   |

| 8     | CRx3A           | Rx / Tx   | 31    | CRx12B          | Rx / Tx   |

| 9     | CRx3B           | Rx / Tx   | 32    | -               | -         |

| 10    | CRx4A           | Rx / Tx   | 33    | CTx1            | N/A       |

| 11    | CRx4B           | Rx / Tx   | 34    | CTx2            | N/A       |

| 12    | CRx4C           | Rx / Tx   | 35    | CTx3            | N/A       |

| 13    | CRx5A           | Rx / Tx   | 36    | CTx4            | N/A       |

| 14    | CRx5B           | Rx / Tx   | 37    | CTx5            | N/A       |

| 15    | CRx6A           | Rx / Tx   | 38    | CTx6            | Tx Only   |

| 16    | CRx6B           | Rx / Tx   | 39    | CTx7            | Tx Only   |

| 17    | CRx6C           | Rx / Tx   | 40    | CTx8            | Tx Only   |

| 18    | CRx7A           | Rx / Tx   | 41    | CTx9            | Tx Only   |

| 19    | CRx7B           | Rx / Tx   | 42    | CTx10           | Tx Only   |

| 20    | CRx8A           | Rx / Tx   | 43    | CTx11           | Tx Only   |

| 21    | CRx8B           | Rx / Tx   | 44    | CTx12           | Tx Only   |

| 22    | CRx8C           | Rx / Tx   | 45    | CTx13           | Tx Only   |

#### Table 6.1: Rx and Tx Selection

It is important to note that a single ProxFusion<sup>®</sup> sampling engine can only sample one input per sampling cycle. Therefore, 'CRx0A' and 'CRx0B' cannot be selected as Rx pins for channels sampled during the same cycle. Channel Rx and Tx pin selections must be configured such that a single sampling engine is used during both cycles to achieve a configuration supporting the maximum number of channels.

When 7 is written to the *Cycle 0 Channel Selection* register and 3 is written to the *Cycle 1 Channel Selection* register, 10 channels are activated, with channels 0-6 in cycle 0 and channels 7-9 in cycle 1. Channels 10-19 are inactive.

# 6.1 Counts

The sensing measurement of each channel returns a relative and unit-less value that is inversely proportional to inductance. This value is referred to as the *Raw Counts* value of a channel. All outputs are derived from *Raw Counts* values.

The maximum value of a *Raw Counts* sample can be defined in the *Hardware Settings* register. This will define a maximum analogue sampling time and may reduce the total sampling time of the device.

The *Linearised Counts* value is derived from the *Raw Counts* value of a channel with the equation below:

$$Linearised Counts = \frac{3276750}{Raw Counts}$$

(5)

A first-order low-pass IIR filter is applied to the *Linearised Counts* of each channel to reduce the highfrequency noise on the *Linearised Counts*. The response of this filter is defined by the *Linearised Counts Normal Power Beta* register when the device is in normal power mode. A higher beta parameter will result in a slower filter response and less noise on the channel.

# 6.2 Automatic Tuning Implementation (ATI)

The ATI of the IQS9320 allows the device to perform optimally with a wide range of external inductance values without the need to modify external components. The ATI is responsible for modifying the *Multiplier and Divider Selection* register of each channel to achieve a *Raw Counts* value equal to the value defined in the *ATI Target* register with some error.

The *ATI Band* register specifies the acceptable error from the *ATI Target*. If the ATI algorithm cannot achieve a *Raw Counts* value within the *ATI Band*, or the *LTA* of a channel drifts outside the valid range defined by the *ATI Band* the device will set the global *ATI Error Flag* in the *System Status* register and the channel-specific *ATI Error Flag* in the *ATI Error Flags* register. The *System Configuration* register can be modified to disable the ATI or configure the device such that the device will automatically re-ATI when the *ATI Error Flag* is set.

$$(ATI Target - ATI Band) < Raw Count < (ATI Target + ATI Band)$$

(6)

$$(ATI Target - ATI Band)_{\text{Linearised}} < LTA < (ATI Target + ATI Band)_{\text{Linearised}}$$

(7)

## 6.3 Reference Tracking (LTA)

The *Long-Term Average (LTA)* value of a channel is determined by applying a first-order low-pass IIR filter to the *Linearised Counts* value of a channel. The *LTA* is used to detect user interaction by providing a reference against which the *Linearised Counts* of a channel can be compared. The *LTA* of a channel should be configured to steadily track changes in the environment while ignoring input caused by user interaction.

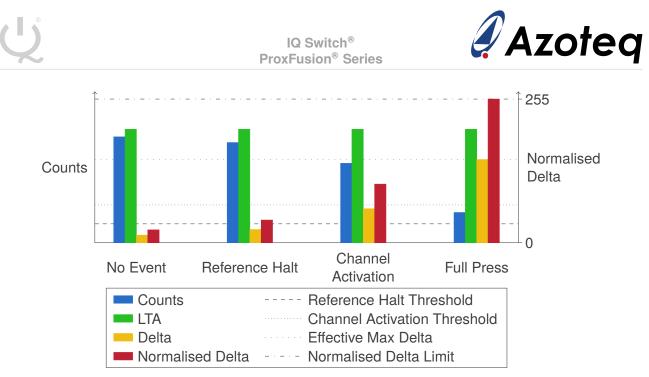

#### 6.3.1 Reference Halt

A *Reference Halt Flag* of a channel is set when the *Normalised Delta* value of a channel exceeds the *Reference Halt Threshold* and will result in the *LTA* value of the channel remaining constant such that user interactions or environmental changes will not affect the reference measurement. The *Reference Halt Flag* of each channel is available in the *Reference Halt Flags* register.

The *Reference Halt* event of each channel has a timeout period defined by the *Reference Halt Timeout* register, which can be adjusted in increments of 255 milliseconds. A reference halt timeout event will result in the device setting the *LTA* value of the relevant channel equal to the *Linearised Counts* value of the channel. The reference halt timeout event can be disabled by writing *0* to the *Reference Halt Timeout* register.

#### 6.3.2 Fast Reference

The fast reference event will occur when the *Normalised Delta* value of a channel is less than the negative value defined in the *Fast Reference Threshold* register. The corresponding *Fast LTA Normal Power Beta* value is used as the LTA filter parameter during a fast reference event when the device is in normal power mode. The *Fast LTA Normal Power Beta* filter parameter should always be less than the *LTA Normal Power Beta* filter parameter.

## 6.4 Delta

The difference between the *Linearised Counts* value and the *LTA* value of each channel is used to determine user interaction. This value is referred to as the *Delta* value of the channel.

$$Delta = LTA - Linearised Counts$$

(8)

#### 6.5 Normalised Delta

The *Delta* value of each channel is normalised against an *Effective Max Delta* value that is adjustable for each channel. The *Normalised Delta* is expressed as an 8-bit fraction of the *Effective Max Delta*. The *Effective Max Delta* values compensate for the variance in sensitivity between inductive channels.

The *Normalised Delta* is used as the final output from which channel events are determined. The *Normalised Delta* values of all channels are compared to the *Activation Threshold*, *Reference Halt Threshold*, and *Fast Reference Threshold* values to set channel flags.

Normalised Delta =

$$\frac{255 \times \text{Delta}}{\text{Effective Max Delta}}$$

(9)

## 6.6 Channel Activation

Channel activation events occur when the *Normalised Delta* value of a channel exceeds the selected *Activation Threshold*. This results in the *Channel Activation Flag* being set. The channel activation event has no timeout period and will cause the channel to remain in activation indefinitely if no external input is given.

The *Deactivation Threshold* of a channel is equal to the value of the *Activation Hysteresis* deducted from the value of the *Activation Threshold*. The original *Activation Threshold* is restored when the *Activation Flag* of the given channel is cleared.

The IQS9320 supports per-key activation threshold selection by setting the *Enable Individual Thresholds* bit in the *System Control* register. The activation threshold of each channel is then defined in the *Individual Activation Thresholds* register.

Figure 6.1: Channel Events

# 6.7 TriggerMax<sup>™</sup>

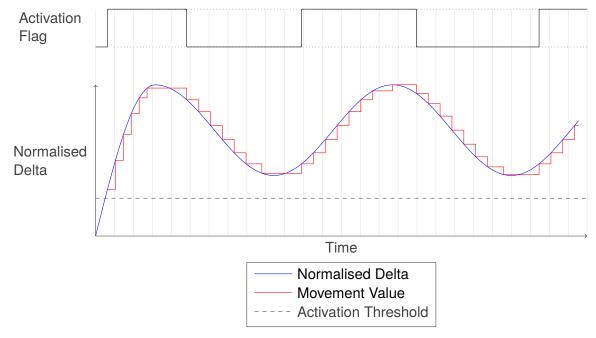

The TriggerMax<sup>™</sup> dynamic actuation UI will track changes in the *Normalised Delta* value of channels for which the *Normalised Delta* exceeds the *Activation Threshold*. The *Movement* value is used to track changes in the *Normalised Delta* of a given channel. The *Movement Threshold* parameter defines the difference between the *Normalised Delta* value and the *Movement* value before a TriggerMax<sup>™</sup> event can occur. A TriggerMax<sup>™</sup> event may set or clear the *Channel Activation Flag* of a given channel and will set the *Movement* value equal to the *Normalised Delta* value. The behaviour of the TriggerMax<sup>™</sup> UI is displayed in figure 6.2.

Figure 6.2: Movement Tracking Behaviour

# 7 GPIO Interface

# 7.1 Key Scan

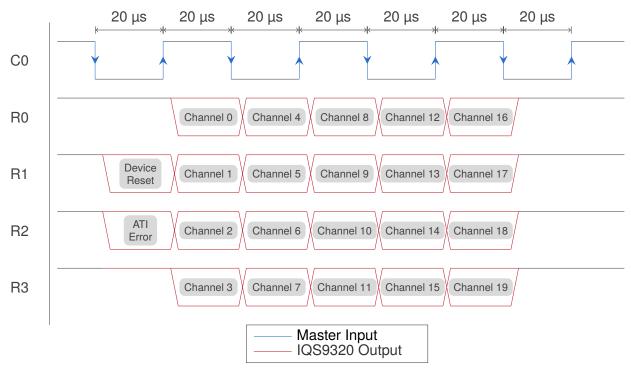

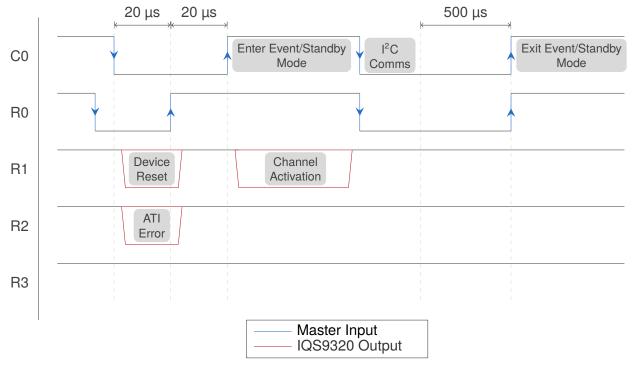

Key scanning can be used to read the *Activation Flags* of all devices in a column simultaneously. The *Device Reset Flag* and *Global ATI Error Flag* states of each device in the column will also be produced as output. The key scanning state is entered with a falling edge produced by the master device on the *C0* pin if the *R0* and *R3* pins are *HIGH*. The master device will produce the *Device Reset Flag* and *Global ATI Error Flag* states on the first falling edge on *C0* and will continue to produce *Channel Activation Flag* states on alternating *C0* edges as indicated in figure 7.1. The number of *C0* edges required to complete the sequence is defined by the number of channels the device is configured for. All channel and device states are active when the associated row output is *LOW*.

Figure 7.1: GPIO Sequence: Key Scan

# 7.2 I<sup>2</sup>C Configuration

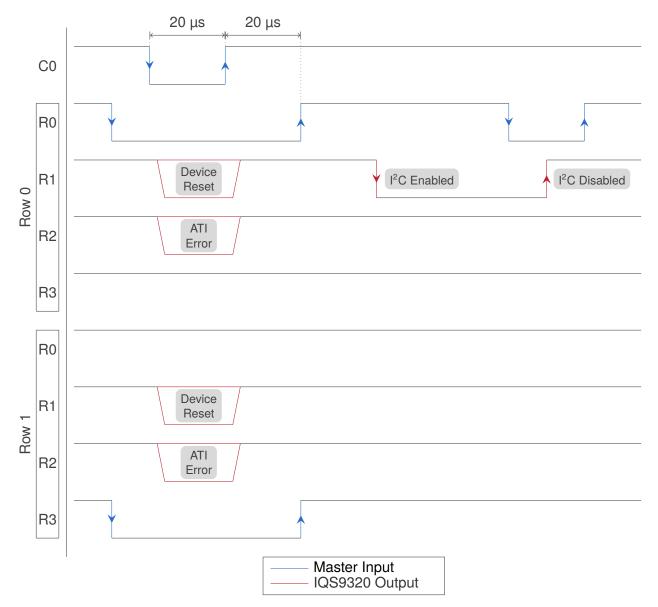

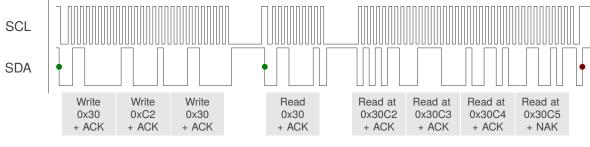

The  $I^2C$  peripheral of a single device in a matrix can be activated at a time for configuration purposes. All devices in the matrix have the same  $I^2C$  device address and require input on the column and row pins to enable communication on the shared  $I^2C$  bus.

The configuration state requires a falling edge on *C0*, with the *R0* pin *LOW* and the *R3* pin *HIGH*. The state is then entered with a rising edge on *C0*. The IQS9320 will then pull the *R1* pin *LOW* to indicate that the  $I^2C$  peripheral is enabled. The *R1* pin will remain *LOW* until the master device exits the configuration state or when the configuration timeout event occurs. To prevent other devices in the column from entering an undesired state, the master device must pull the *R3* pin *LOW* on selected devices. This behaviour is displayed in figure 7.2.

The *GPIO Sequence Configuration Timeout Period* register can be adjusted to select a timeout value between 1 and 255 milliseconds. The configuration timer is restarted when entering the configuration state, or when a valid  $I^2C$  transaction occurs.

Figure 7.2: GPIO Sequence: I<sup>2</sup>C Configuration

# 7.3 Event/Standby Mode

The IQS9320 can enter a low-power state during which GPIO sequences are disabled. The device will either enter *Event Mode* or *Standby Mode* depending on the state of the *Enable Event Mode* bit in the *System Configuration* register. While in standby mode, the device will consume a minimal amount of power and will not complete any channel samples.

While in event mode, the device will sample channels at a rate defined by the *ULP Sample Interval* register. During *Event Mode*, the device will indicate channel activation events by pulling the *R1* pin (GPIO12) *LOW*. The *Event Mode* state will result in reduced power consumption when compared to the normal operating mode configured for the GPIO interface.

The event/standby mode sequence is started with a falling edge on the *C0* pin while the *R0* pin is *LOW* and the *R3* pin is *HIGH*. The state is then entered with a rising edge on the *R0* pin followed by a rising edge on the *C0* pin. The state is then exited with a valid  $I^2C$  transaction while the *C0* and *R0* pins are *LOW*. The *C0* and *R0* pins must be kept *LOW* for a minimum of 500µs after completing the  $I^2C$  transaction.

Figure 7.3: GPIO Sequence: Event/Standby

# 8 Power Modes

#### 8.1 Mode Selection

The IQS9320 has 3 power mode selection options with an additional automatic power mode option for switching between power modes without the need for commands from a master device. The power mode can be selected in the *System Control* register.

- > Normal Power

- > Low Power

- > Ultra-Low Power

- > Automatic Power Modes

## 8.2 Mode Parameters

The IQS9320 has 2 power mode parameters that define the sample rate, current consumption, and automatic power mode behaviour.

- > Sample Interval

- > Mode Timeout

The sample interval parameter defines in milliseconds the period between samples and is responsible for the resulting current consumption of the device. It is recommended to configure the IQS9320 such that the sample interval increases as a lower power mode is selected.

Given that the automatic power mode is selected, the mode timeout parameter defines in milliseconds the period for which the device will remain in a given power mode before a lower mode is automatically selected.

## 8.3 Automatic Power Modes

The automatic power mode of the device will cause the device to lower the active power mode when no wake-up event occurs during the period defined by the *Mode Timeout* parameter of the active power mode. The device may enter the 'Ultra-Low Power' mode where it will remain until a wake-up event occurs or the master device modifies the power mode selection.

A wake-up event can be caused by a channel activation or I<sup>2</sup>C event and will result in the device returning to the 'Normal Power Mode' where it will remain for the duration of the *Normal Power Mode Timeout* if no other wake-up event occurs. The active wake-up events can be modified in the *System Configuration* register.

## 8.4 Standby Mode

The IQS9320 supports a standby mode that can be entered by setting the *Standby Mode* bit in the *System Control* register or by executing the associated GPIO input sequence. No analogue sampling or digital processing occurs while the device is in standby mode, resulting in very low current consumption. The device will respond to I<sup>2</sup>C instructions such that the *System Control* register can be modified and the device can exit standby mode.

# 9 Additional Features

#### 9.1 Reset Indication

At startup, or after a reset, the reset flag will be set in the *System Status* register. The master device can acknowledge the reset by setting the *Acknowledge Reset* bit in the *System Control* register. If the *Reset Flag* bit is set again after being acknowledged, the master device will know a reset has occurred and can act accordingly.

The master device can reset the IQS9320 by setting the *Software Reset* bit in the *System Control* register or by pulling the *MCLR* pin *LOW* as described in section 4.5.

The *Enable Reset Pin* bit in the *System Configuration* register is used to configure the reset pin, GPIO13, as an open-drain active-low output to indicate that the *Reset Flag* is set in the *System Status* register.

## 9.2 Event Pin

The *Enable Event Pin* bit in the *System Configuration* register is used to configure the event pin, GPIO14, as an open-drain active-low output to indicate that the *Activation Flag* has been set in the *System Status* register. This event pin is only available for devices configured for an I<sup>2</sup>C interface.

This will allow the IQS9320 device to communicate user interaction to the master device with minimal delay and no action required from the master device.

#### 9.3 Manual Calibration

The *Sampled Max Delta* register tracks the largest *Delta* values observed by each channel when the *Sample Max Counts* bit is set in the *System Control* register.

The Sampled Max Delta value is used to express the total travel range of a key after that key has been fully pressed. The Sampled Max Delta value can then be written to the Effective Max Delta register, such that the Normalised Delta value of a channel will express the full range of the key press. The Sampled Max Delta values will be written to the Effective Max Delta register when the Apply Sampled Max Delta bit is set in the System Control register.

**Note** : For more information regarding the calibration procedure, please refer to application note AZD140 : IQS9320 Keyboard Production Testing Procedure.

## 9.4 External Clock Input

The IQS9320 can be configured to use an external clock input for the ProxFusion<sup>®</sup> modules by setting the *Enable External POSC Clock Source* bit in the *System Configuration* register. The clock source should be provided as a square wave with a 50% duty cycle, peak-to-peak voltage of 3.3V, DC offset voltage of 1.65V, and a maximum frequency of 16MHz.

The *External Clock Active* bit in the *System Status* register will be set when the system is actively using the external clock. The device will not use the external clock source if any channel Tx pins are configured as CTx12 or CTx13.

The *External POSC Clock Output* pin (CTx12) will be *HIGH* when the clock source must be active.

# 10 I<sup>2</sup>C Interface

#### 10.1 Module Specification

The device supports a standard two-wire  $I^2C$  interface with a maximum bit rate of up to 1Mbps. The memory structures accessible over the  $I^2C$  interface are byte-addressable with 16-bit address values. 16-bit or 32-bit values are packed with little-endian byte order and are stored in word-aligned addresses.

- > Standard two-wire interface

- > Fast-Mode Plus I<sup>2</sup>C with up to 1Mbps bit rate

- > 7-bit device address

- > 16-bit register address

- > Little-endian

The master device may use the I<sup>2</sup>C interface to read or write data at any time. The device will exit a sleep condition when I<sup>2</sup>C transactions occur while the device is in a low-power mode and may be configured to return to normal power when automatic power modes are enabled.

## **10.2** I<sup>2</sup>C Address Options

The IQS9320 supports 8 different 7-bit device address options which can be selected by setting the state of the 3 address selection pins. The default device address options are listed in Table 10.1.

| Address Select<br>2 | Address Select<br>1 | Address Select<br>0 | 7-bit Device<br>Address | 8-bit Read<br>Address | 8-bit Write<br>Address |

|---------------------|---------------------|---------------------|-------------------------|-----------------------|------------------------|

| LOW                 | LOW                 | LOW                 | 0x30                    | 0x61                  | 0x60                   |

| LOW                 | LOW                 | HIGH                | 0x32                    | 0x65                  | 0x64                   |

| LOW                 | HIGH                | LOW                 | 0x34                    | 0x69                  | 0x68                   |

| LOW                 | HIGH                | HIGH                | 0x36                    | 0x6D                  | 0x6C                   |

| HIGH                | LOW                 | LOW                 | 0x38                    | 0x71                  | 0x70                   |

| HIGH                | LOW                 | HIGH                | 0x3A                    | 0x75                  | 0x74                   |

| HIGH                | HIGH                | LOW                 | 0x3C                    | 0x79                  | 0x78                   |

| HIGH                | HIGH                | HIGH                | 0x3E                    | 0x7D                  | 0x7C                   |

#### Table 10.1: I<sup>2</sup>C addressing options

#### **10.3 Memory Management**

The IQS9320 can be addressed and configured over I<sup>2</sup>C at any time and therefore requires 2 configuration memory structures. One structure is actively used for sampling and processing channel data, while the other is always available to a master device via the I<sup>2</sup>C peripheral. The modifications made to the memory structure available over I<sup>2</sup>C will not affect the sampling and processing of channel data until the *Reconfigure Device* bit has been set in the *System Control* register.

This affects all read/write registers excluding the *System Control* register which is monitored after each cycle. The read-only registers will always contain the latest data available to the device.

# 10.4 Read and Write Operations

#### 10.4.1 I<sup>2</sup>C Read From Specific Address

The read operation is displayed in Figure 10.1. The master will first provide a start condition followed by the device address with a write command. The IQS9320 will respond with an acknowledgement after which the master device will transmit two bytes defining the register address. The master will then send a repeated start condition followed by the device address with a read command. The IQS9320 will then transmit data from the requested address and will continue to do so while the master acknowledges each byte. The read operation is ended when the master does not acknowledge the last byte received and produces a stop condition.

Figure 10.1: I2C read example

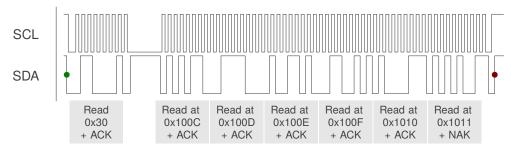

#### 10.4.2 I<sup>2</sup>C Read From Default Address

The *Default Read Address* register defines a default I<sup>2</sup>C read address such that no write operation is required prior to reading data from the IQS9320. The master will first provide a start condition followed by the device address with a read command. The IQS9320 will respond with an acknowledgement followed by the first byte of data read from the default address. The IQS9320 will continue to transmit data from the initial default read address while the master acknowledges each byte. The read operation is ended when the master does not acknowledge the last byte received and produces a stop condition. This operation is displayed with a default read address of 0x100C in Figure 10.2.

Figure 10.2: I2C read default address example

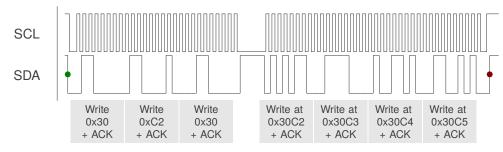

## 10.4.3 I<sup>2</sup>C Write To Specific Address

The write operation is displayed in Figure 10.3. The master will first provide a start condition followed by the device address with a write command. The IQS9320 will respond with an acknowledgement after which the master device will transmit two bytes defining the register address. The slave acknowledges the register address bytes. The master may then write a series of bytes to the register address and the addresses which follow, with each byte being acknowledged by the slave. The write operation is ended when the master produces a stop condition.

# **11 Ordering Information**

## 11.1 Ordering Code

<u>IQS9320</u> <u>zzz</u> ppb

#### Table 11.1: Ordering Code Description

| Description    | Placeholder |       | Options                                                                                          |

|----------------|-------------|-------|--------------------------------------------------------------------------------------------------|

| Description    | Placenoider | Value | Description                                                                                      |

| Configuration  |             | 000   | 20-key Configuration<br>I <sup>2</sup> C Interface<br>I <sup>2</sup> C Address Range = 0x30-0x3E |

| Configuration  | ZZZ         | 001   | 20-key Configuration<br>GPIO Interface<br>I <sup>2</sup> C Address = 0x30                        |

| Package Type   | рр          | QF    | QFN-52 Package                                                                                   |

| Bulk Packaging | b           | R     | QFN-52 Reel (3000pcs/reel)                                                                       |

#### Example : IQS9320-000QFR

## 11.2 QFN52 Top Markings

Figure 11.2: QFN52 Generic Package Top Marking

# 12 QFN52 Package Information

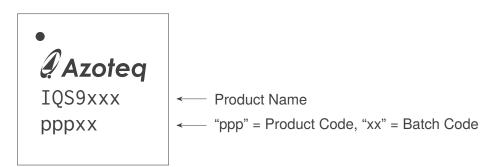

## 12.1 QFN52 Package Outline

Figure 12.1: QFN52 Package Outline Visual Description

#### Table 12.1: QFN52 Package Dimensions [mm]

| Dimension | Millimeters    |          |      |  |  |  |

|-----------|----------------|----------|------|--|--|--|

| Dimension | Min            | Тур      | Мах  |  |  |  |

| А         | 0.70           | 0.75     | 0.80 |  |  |  |

| A1        | 0.00 0.02 0.05 |          |      |  |  |  |

| A3        | 0.20 REF       |          |      |  |  |  |

| D         | 6.00 BSC       |          |      |  |  |  |

| E         |                | 6.00 BSC |      |  |  |  |

| D2        | 4.40           | 4.50     | 4.60 |  |  |  |

| E2        | 4.40           | 4.50     | 4.60 |  |  |  |

| b         | 0.15           | 0.20     | 0.25 |  |  |  |

| е         |                | 0.40 BSC |      |  |  |  |

| L         | 0.35           | 0.40     | 0.45 |  |  |  |

#### Table 12.2: QFN52 Package Tolerances [mm]

| Tolerance | Millimeters |

|-----------|-------------|

| bbb       | 0.10        |

| ddd       | 0.05        |

| eee       | 0.08        |

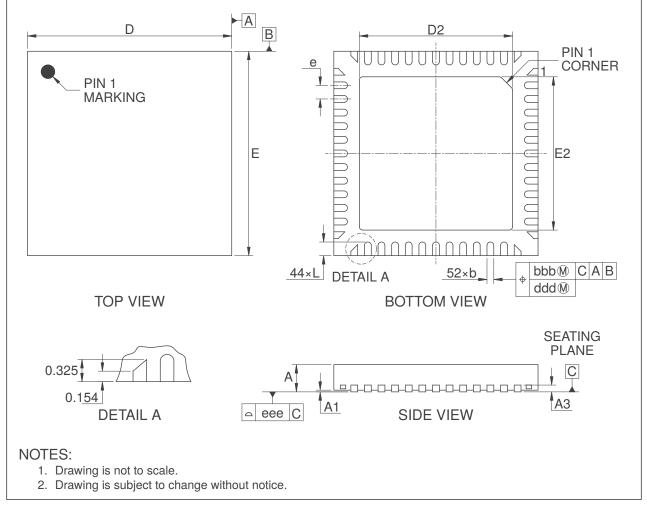

#### 12.2 QFN52 Recommended Footprint

Figure 12.2: QFN52 Recommended Footprint

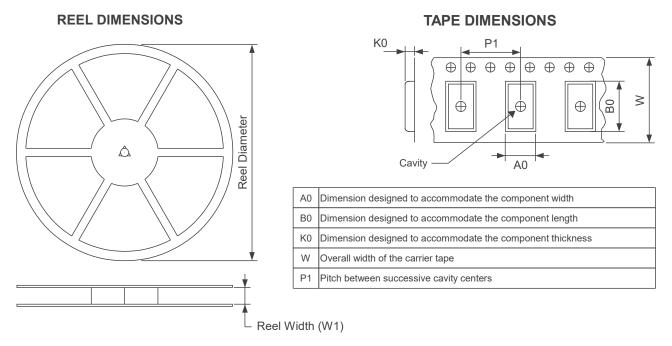

# 12.3 Tape and Reel Specifications

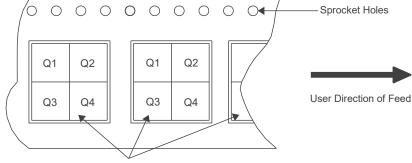

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Pocket Quadrants

Figure 12.3: Tape and Reel Specification

| Table 12.3: | Tape and | Reel Specifications |

|-------------|----------|---------------------|

|-------------|----------|---------------------|

| Paakaga              |                  |               | Dimension [Millimeters] |     |     |            |      |                   |    |

|----------------------|------------------|---------------|-------------------------|-----|-----|------------|------|-------------------|----|

| Package<br>Type Pins | Reel<br>Diameter | Reel<br>Width | <b>A</b> 0              | B0  | K0  | <b>P</b> 1 | W    | Pin 1<br>Quadrant |    |

| QFN52                | 52               | 330.0         | 16.4                    | 6.3 | 6.3 | 1.1        | 12.0 | 16.0              | Q2 |

# 13 I<sup>2</sup>C Memory Map

| Address    | Length | Description                                 | Default    | Notes       |

|------------|--------|---------------------------------------------|------------|-------------|

| Read Only  |        | Version Information                         |            |             |

| 0x0000     | 2      | Product Number                              | 0x0716     |             |

| 0x0002     | 2      | Product Major Version                       | 0x0001     |             |

| 0x0004     | 2      | Product Minor Version                       | 0x0000     |             |

| 0x0006     | 4      | Product SHA                                 | 0x0E90D1EB |             |

| 0x000A     | 2      | Library Number                              | 0x037D     |             |

| 0x000C     | 2      | Library Major Version                       | 0x0001     |             |

| 0x000E     | 2      | Library Minor Version                       | 0x0000     |             |

| 0x0010     | 4      | Library SHA                                 | 0x47B24D3E |             |

| 0x0014     | 6      | Unique Identifier                           | -          |             |

| Read Only  |        | Device Data                                 |            |             |

| 0x1000     | 2      | System Status                               | 0x0040     | Table A.1   |

| 0x1002     | 4      | ATI Error Flags                             | -          | Table A.2   |

| 0x1006     | 4      | Reference Halt Flags                        | -          | Table A.3   |

| 0x100A     | 4      | Activation Flags                            | -          | Table A.4   |

| 0x100E     | 20     | Normalised Delta                            | -          | uint8 [20]  |

| 0x1022     | 20     | Movement                                    | -          | uint8 [20]  |

| 0x1036     | 40     | Delta                                       | -          | int16 [20]  |

| 0x105E     | 40     | Counts                                      | -          | uint16 [20] |

| 0x1086     | 40     | LTA                                         | -          | uint16 [20] |

| 0x10AE     | 40     | Raw Counts                                  | -          | uint16 [20] |

| Read-Write |        | Device Configuration                        |            |             |

| 0x2000     | 2      | System Control                              | 0x0000     | Table A.5   |

| 0x2002     | 2      | System Configuration                        | 0x5E0B     | Table A.6   |

| 0x2004     | 2      | Normal Power Sampling Interval              | 0x0000     | ms          |

| 0x2006     | 2      | Normal Power Timeout                        | 0x1388     | ms          |

| 0x2008     | 2      | Low Power Sampling Interval                 | 0x0028     | ms          |

| 0x200A     | 2      | Low Power Timeout                           | 0x1388     | ms          |

| 0x200C     | 2      | Ultra-Low Power Sampling Interval           | 0x0050     | ms          |

| 0x200C     | 2      | Ultra-Low Power Timeout                     | 0x0000     | ms          |

| 0x2010     | 2      | Default Read Address                        | 0x100A     |             |

| 0x2012     | 1      | GPIO Sequence Timeout Period                | 0x0A       | ms          |

| 0x2013     | 1      | GPIO Sequence Configuration Timeout Period  | 0x14       | ms          |

| 0x2014     | 2      | I <sup>2</sup> C Transaction Timeout Period | 0x00C8     | ms          |

| Read-Write |        | Channel Configuration                       |            |             |