## LCD / LCM SPECIFICATION

## 曜凌光電股份有限公司 Raystar Optronics, Inc.

T: +886-4-2565-0761 | F: +886-4-2565-0760 salescontact@raystar-optronics.com | www.raystar-optronics.com

### RX12864D2

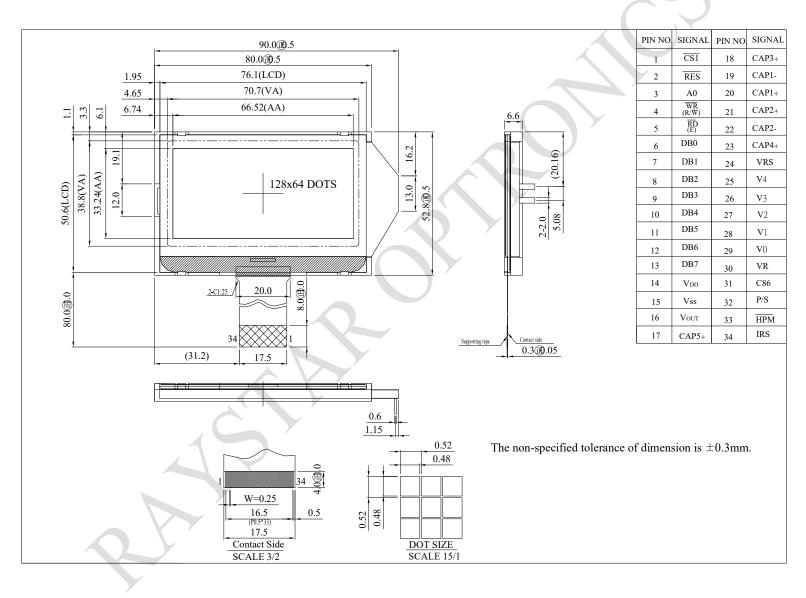

#### **General Specification**

- Module dimension: 90.0 x 52.8 x 6.6 mm

- View area: 70.7 x 38.8 mm

- Active area: 66.52 x 33.24 mm

- Number of Dots: 128 x 64

- Dot size: 0.48 x0.48 mm

- Dot pitch: 0.52 x 0.52 mm

- Duty: 1/64, 1/9 Bias

- Backlight Type: LED

- IC: ST7565P

#### **Interface Pin Function**

| Pin No. | Symbol   | Level  | Description                                                                                                               |

|---------|----------|--------|---------------------------------------------------------------------------------------------------------------------------|

|         |          |        | This is the chip select signal. When /CS1 = "L" , then the                                                                |

| 1       | /CS1     |        | chip select becomes active, and data/command I/O is                                                                       |

|         |          |        | enabled.                                                                                                                  |

| 2       | /RES     |        | When /RES is set to "L" , the settings are initialized.                                                                   |

|         |          |        | This is connect to the least significant bit of the normal MPU                                                            |

|         |          |        | address bus, and it determines whether the data bits are data                                                             |

| 3       | A0       |        | or a command.                                                                                                             |

|         |          |        | A0 = "H": Indicates that D0 to D7 are display data.                                                                       |

|         |          |        | A0 = "L": Indicates that D0 to D7 are control data.                                                                       |

|         |          |        | When connected to an 8080 MPU, this is active LOW.                                                                        |

|         |          |        | (R/W) This terminal connects to the 8080 MPU /WR signal.<br>The signals on the data bus are latched at the rising edge of |

| 4       | /WR(R/W) |        | the /WR signal.                                                                                                           |

|         |          |        | When connected to a 6800 Series MPU:                                                                                      |

|         |          |        | This is the read/write control signal input terminal.                                                                     |

|         |          |        | When R/W = "H": Read.                                                                                                     |

|         |          |        | When R/W = "L": Write.                                                                                                    |

|         | /RD(E)   |        | When connected to an 8080 MPU, this is active LOW.                                                                        |

|         |          |        | (E) This pin is connected to the /RD signal of the 8080 MPU,                                                              |

| 5       |          |        | and the ST7565P series data bus is in an output status when                                                               |

|         |          |        | this signal is "L".                                                                                                       |

|         |          |        | When connected to a 6800 Series MPU, this is active HIGH.                                                                 |

| 0       |          | $\sim$ | This is the 6800 Series MPU enable clock input terminal.                                                                  |

| 6       | DB0      |        |                                                                                                                           |

| 7       | DB1      |        |                                                                                                                           |

| 8       | DB2      |        | This is an 8-bit bi-directional data bus that connects to an 8-                                                           |

| 9       | DB3      |        | bit or 16-bit standard MPU data                                                                                           |

| 10      | DB4      |        | Bus.                                                                                                                      |

| 11      | DB5      |        |                                                                                                                           |

| 12      | DB6      |        |                                                                                                                           |

| 13      | DB7      |        |                                                                                                                           |

| 14      | VDD      |        | Shared with the MPU power supply terminal VDD.(3.3 V)                                                                     |

| 15      | VSS      |        | This is a 0V terminal connected to the system GND.                                                                        |

| 16  | VOUT  | DC/DC voltage converter. Connect a capacitor between this                                                                                                                           |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |       | terminal and VSS.                                                                                                                                                                   |

| 17  | CAP5+ | DC/DC voltage converter. Connect a capacitor between this                                                                                                                           |

|     | 0,4 0 | terminal and the CAP1- terminal.                                                                                                                                                    |

| 18  | CAP3+ | DC/DC voltage converter. Connect a capacitor between this                                                                                                                           |

| 10  |       | terminal and the CAP1- terminal.                                                                                                                                                    |

| 19  |       | DC/DC voltage converter. Connect a capacitor between this                                                                                                                           |

| 19  | CAP1- | terminal and the CAP1+ terminal.                                                                                                                                                    |

|     |       | DC/DC voltage converter. Connect a capacitor between this                                                                                                                           |

| 20  | CAP1+ | terminal and the CAP1- terminal.                                                                                                                                                    |

| 0.1 | CAP2+ | DC/DC voltage converter. Connect a capacitor between this                                                                                                                           |

| 21  |       | terminal and the CAP2- terminal.                                                                                                                                                    |

|     |       | DC/DC voltage converter. Connect a capacitor between this                                                                                                                           |

| 22  | CAP2- | terminal and the CAP2+ terminal.                                                                                                                                                    |

|     | CAP4+ | DC/DC voltage converter. Connect a capacitor between this                                                                                                                           |

| 23  |       | terminal and the CAP2- terminal.                                                                                                                                                    |

|     | VRS   | This is the externally-input VREG power supply for the LCD                                                                                                                          |

| 24  |       | power supply voltage regulator.                                                                                                                                                     |

| 25  | V4    | This is a multi-level power supply for the liquid crystal drive.                                                                                                                    |

| 26  | V3    | The voltage Supply applied is determined by the liquid crystal                                                                                                                      |

| 20  | V3    | cell, and is changed through the use of a resistive voltage                                                                                                                         |

| 27  | V2    | divided or through changing the impedance using an op. amp.                                                                                                                         |

|     |       | Voltage levels are determined based on Vss, and must                                                                                                                                |

| 28  | V1    | maintain the relative magnitudes shown below.                                                                                                                                       |

|     |       | $V0 \ge V1 \ge V2 \ge V3 \ge V4 \ge Vss$                                                                                                                                            |

|     |       | When the power supply turns ON, the internal power supply                                                                                                                           |

|     |       | circuits produce the V1 to V4 voltages shown below. The                                                                                                                             |

|     | VO    | voltage settings are selected using the LCD bias set                                                                                                                                |

| 29  |       | command.                                                                                                                                                                            |

|     |       | 1/65 DUTY 1/49 DUTY 1/33 DUTY 1/55 DUTY 1/53 DUTY                                                                                                                                   |

|     |       | V1 8/9*V0,6/7*V0 7/8*V0,5/6*V0 5/6*V0 7/8*V0,5/6*V0 7/8*V0,5/6*V0 7/8*V0,5/6*V0 7/8*V0,5/6*V0 7/8*V0,5/6*V0 2 7/9*V0,5/7*V0 6/8*V0,4/6*V0 4/6*V0,3/5*V0 6/8*V0,4/6*V0 6/8*V0,4/6*V0 |

|     |       | V3 2/9*V0,2/7*V0 2/8*V0,2/6*V0 2/6*V0,2/5*V0 2/8*V0,2/6*V0 2/8*V0,2/6*V0   V4 1/9*V0,1/7*V0 1/8*V0,1/6*V0 1/6*V0,1/5*V0 1/8*V0,1/6*V0 1/8*V0,1/6*V0                                 |

|     |       | Output voltage regulator terminal. Provides the voltage                                                                                                                             |

|     | VR    | between VDD and V5 through a resistive voltage divider.                                                                                                                             |

|     |       | IRS = "L" : the V5 voltage regulator internal resistors are not                                                                                                                     |

| 30  |       | used .                                                                                                                                                                              |

|     |       | IRS = "H" : the V5 voltage regulator internal resistors are                                                                                                                         |

|     |       | used .                                                                                                                                                                              |

|     |       |                                                                                                                                                                                     |

|     |      | 1                                                                  |  |  |  |  |

|-----|------|--------------------------------------------------------------------|--|--|--|--|

|     | _    | This is the MPU interface switch terminal.                         |  |  |  |  |

| 31  | C86  | C86 = "H": 6800 Series MPU interface.                              |  |  |  |  |

|     |      | C86 = "L": 8080 MPU interface.                                     |  |  |  |  |

|     |      | This is the parallel data input/serial data input switch terminal. |  |  |  |  |

|     |      | P/S = "H": Parallel data input.                                    |  |  |  |  |

|     |      | P/S = "L": Serial data input.                                      |  |  |  |  |

|     |      | The following applies depending on the P/S status:                 |  |  |  |  |

|     |      | P/S Data/Command Data Read/Write Serial Clock                      |  |  |  |  |

| 32  | P/S  | "H" A0 D0 to D7 RD, WR X                                           |  |  |  |  |

|     |      | L' A0 SI (07) Write only SCL (06)                                  |  |  |  |  |

|     |      |                                                                    |  |  |  |  |

|     |      | When P/S = "L", D0 to D5 may be "H", "L" or Open.                  |  |  |  |  |

|     |      | RD (E) and WR (R/W) are fixed to either "H" or "L".                |  |  |  |  |

|     |      | With serial data input, It is impossible read data from RAM .      |  |  |  |  |

|     | /HPM | This is the power control terminal for the power supply circuit    |  |  |  |  |

| 33  |      | for liquid crystal drive.                                          |  |  |  |  |

|     |      | HPM = "H": Normal mode                                             |  |  |  |  |

|     |      | HPM = "L": High power mode                                         |  |  |  |  |

|     |      | This terminal selects the resistors for the V5 voltage level       |  |  |  |  |

|     | IRS  | adjustment.                                                        |  |  |  |  |

| 34  |      | IRS = "H": Use the internal resistors                              |  |  |  |  |

| 0.1 |      | IRS = "L": Do not use the internal resistors. The V5 voltage       |  |  |  |  |

|     |      | level is regulated by an external resistive voltage divider        |  |  |  |  |

|     |      | attached to the VR terminal                                        |  |  |  |  |

|     |      |                                                                    |  |  |  |  |

|     |      |                                                                    |  |  |  |  |

|     |      |                                                                    |  |  |  |  |

|     |      |                                                                    |  |  |  |  |

|     |      |                                                                    |  |  |  |  |

|     |      |                                                                    |  |  |  |  |

|     |      |                                                                    |  |  |  |  |

|     |      |                                                                    |  |  |  |  |

|     |      |                                                                    |  |  |  |  |

| )   |      |                                                                    |  |  |  |  |

|     |      |                                                                    |  |  |  |  |

#### **Contour Drawing**

#### **Absolute Maximum Ratings**

| ltem                                | Symbol         | Min  | Тур | Max    | Unit |

|-------------------------------------|----------------|------|-----|--------|------|

| Operating Temperature               | Тор            | -20  | _   | +70    | °C   |

| Storage Temperature                 | Тѕт            | -30  | _   | +80    | °C   |

| Power Supply Voltage                | VDD            | -0.3 | _   | 3.6    | v    |

| Power supply voltage (VDD standard) | V0, VOUT       | -0.3 |     | 14.5   | V    |

| Power supply voltage (VDD standard) | V1, V2, V3, V4 | -0.3 | )_> | V0+0.3 | V    |

# **Electrical Characteristics**

| ltem                                        | Symbol                           | Condition             | Min                 | Тур  | Мах                 | Unit |

|---------------------------------------------|----------------------------------|-----------------------|---------------------|------|---------------------|------|

| Supply Voltage For Logic                    | V <sub>DD</sub> -V <sub>SS</sub> | _                     | 2.7                 | 3.0  | 3.3                 | V    |

|                                             |                                  | Ta=-20°C              | 10.0                | 10.2 | 10.4                | V    |

| Supply Voltage For LCM                      | V <sub>0</sub> -V <sub>SS</sub>  | Ta=25°C               | 9.8                 | 10.0 | 10.2                | V    |

|                                             |                                  | Ta=70℃                | 9.6                 | 9.8  | 10.0                | V    |

| Input High Volt.                            | Vін                              | _                     | 0.8 V <sub>DD</sub> | _    | Vdd                 | V    |

| Input Low Volt.                             | VIL                              | _                     | Vss                 | _    | 0.2 V <sub>DD</sub> | V    |

| Output High Volt.                           | V <sub>OH</sub>                  | _                     | 0.8 V <sub>DD</sub> | _    | V <sub>DD</sub>     | V    |

| Output Low Volt.                            | V <sub>OL</sub>                  | _                     | Vss                 | _    | 0.2V <sub>DD</sub>  | V    |

| Supply Current(No include<br>LED Backlight) | lod                              | V <sub>DD</sub> =3.0V | _                   | 0.6  | 1                   | mA   |