# NSSHNBO

# 42 V Input Power Management IC with Battery Voltage Detector

No.EA-501-220310

### OVERVIEW

The R5117x is a Power Management IC featuring input voltage range from 3.5V to 42V. This IC includes Battery Voltage Detector, SENSE Voltage Detector and 500 mA Voltage Regulator in a single chip.

#### **KEY BENEFITS**

- Reducing components and improving functional safety

- The Battery Voltage Detector suitable for Early Warning System against battery voltage reduction

- Preventing the false detection of transient characteristic fluctuations by high-speed response Voltage Regulator

#### **KEY SPECIFICATIONS**

- Input Voltage Range (Max. rating): 3.5 V to 42.0 V (50.0 V)

- Supply Current: Typ. 35 μA

#### Voltage Regulator (VR)

- Output Voltage Range: 3.3 V to 5.0 V

- Output Voltage Accuracy:

-1.25% to 0.75%(−40°C ≤Ta≤ 105°C)

- Output Current: 500 mA

- Protection: Thermal shutdown (Detection Temp. Typ.175 °C) Output current (Typ.750 mA) Output short-circuit (Typ.105 mA)

#### SENSE Voltage Detector (SVD)

- Detector Threshold: 2.5 V to 5.0 V (in 0.01V step)

- Detector Threshold Accuracy:

- -1.25% to 0.75%(−40°C ≤Ta≤ 105°C)

- Release hysteresis: max 0.7%

#### **Battery Voltage Detector (BVD)**

- Detector Threshold: 3.5 V to 12.0 V (in 0.1V step)

- Detector Threshold Accuracy:

- -2.0% to 1.0% (−40°C ≤Ta≤ 105°C)

- Release hysteresis: max 5.0%

#### PACKAGES

5.2 x 6.2 x 1.45 (mm)

HQFN0808-28 8.8 x 8.8 x 0.95 (mm)

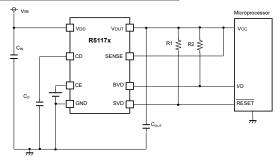

#### **TYPICAL APPLICATIONS**

- CIN: 1.0μF, COUT: 10μF, Ceramic capacitors

- C<sub>D</sub>: Ceramic capacitors for setting detection delay time

#### **SELECTION GUIDE**

| Product Name     | Package     | Quantity<br>per Reel |

|------------------|-------------|----------------------|

| R5117SxxxA-E2-FE | HSOP-8E     | 1,000 pcs            |

| R5117LxxxA-TR-FE | HQFN0808-28 | 2,000 pcs            |

xxx: Specify the set output voltage for VR (V<sub>VRSET</sub>), the set Battery voltage detector threshold (V<sub>BVSET</sub>) and the set SENSE voltage detector threshold (V<sub>SVSET</sub>) by using serial numbers starting from 001

Refer to ELECTRICAL CHARACTERISTICS for detail information.

### APPLICATIONS

- Household electric appliances such as Refrigerators, Rice Cookers and Electric Kettles

- Laptop PCs, Digital Cameras, Digital TVs, Phones and LAN Systems

# **SELECTION GUIDE**

The set output voltages are user-selectable options.

| Product Name     | Product Name Package |           | Pb Free | Halogen Free |  |

|------------------|----------------------|-----------|---------|--------------|--|

| R5117SxxxA-E2-FE | HSOP-8E              | 1,000 pcs | Yes     | Yes          |  |

| R5117LxxxA-TR-FE | HQFN0808-28          | 2,000 pcs | Yes     | Yes          |  |

xxx: Specify the set output voltage for Voltage Regulator (VVRSET),

the set Battery voltage detector threshold ( $V_{BVSET}$ ) and the set SENSE voltage detector threshold ( $V_{SVSET}$ ) by using serial numbers starting from 001<sup>(1)</sup>

Refer to ELECTRICAL CHARACTERISTICS for detail information

$<sup>^{(1)}</sup>$  The combinations of  $V_{\text{VRSET}},\,V_{\text{BVSET}},\,V_{\text{SVSET}}$  are following conditions;

V<sub>VRSET</sub> = 3.3 V to 5.0 V

<sup>•</sup> V<sub>BVSET</sub> = 3.5 V to 12.0 V

<sup>•</sup> V<sub>SVSET</sub> = 2.5 V to 5.0 V

R5117x No.EA-501-220310

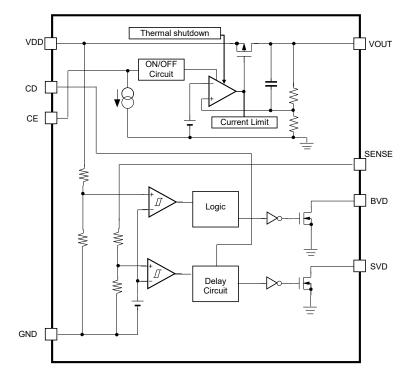

# **BLOCK DIAGRAM**

R5117xxx Block Diagram

# **PIN DESCRIPTION**

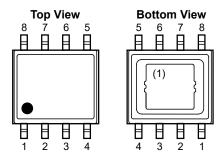

**R5117S (HSOP-8E) Pin Configuration**

### R5117S (HSOP-8E)

| Pin No. | No. Symbol Description |                                                                     |  |  |  |  |

|---------|------------------------|---------------------------------------------------------------------|--|--|--|--|

| 1       | VDD                    | Supply Voltage Pin                                                  |  |  |  |  |

| 2       | CD                     | Pin for setting VD Release Output Delay Time (power-on reset time)  |  |  |  |  |

| 3       | CE                     | Chip Enable Pin (Active-high)                                       |  |  |  |  |

| 4       | GND                    | Ground Pin                                                          |  |  |  |  |

| 5       | SVD                    | SENSE Voltage Reduction Detection Output Pin ("Low" at detection)   |  |  |  |  |

| 6       | BVD                    | Battery Voltage Reduction Detection Output Pin ("Low" at detection) |  |  |  |  |

| 7       | SENSE                  | SENSE Input Voltage Pin                                             |  |  |  |  |

| 8       | VOUT                   | Regulator Output Pin                                                |  |  |  |  |

<sup>&</sup>lt;sup>(1)</sup> The tab on the bottom of the package is substrate level (GND). It is recommended that the tab be connected to the ground plane on the board.

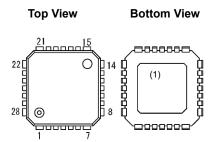

### R5117L(HQFN0808-28) Pin Configuration

#### R5117L(HQFN0808-28)

| Pin No. | Symbol    |                     | Description                                        |

|---------|-----------|---------------------|----------------------------------------------------|

| 1       | Tab (GND) | Tab                 | ※Internally shorted to the GND                     |

| 2       | NC        | No Connection       |                                                    |

| 3       | VDD       | Power Supply Pin    | ※Internally shorted to the 4Pin                    |

| 4       | VDD       | Power Supply Pin    | ※Internally shorted to the 3Pin                    |

| 5       | NC        | No Connection       |                                                    |

| 6       | CD        | Voltage Detector Re | set Delay Time (Power-on Reset Time) Setting Pin   |

| 7       | Tab (GND) | Tab                 | ※Internally shorted to the GND                     |

| 8       | Tab (GND) | Tab                 | ※Internally shorted to the GND                     |

| 9       | CE        | Chip Enable Pin, Ac | tive-high                                          |

| 10      | NC        | No Connection       |                                                    |

| 11      | GND       | Ground Pin          | ※Internally shorted to the 12Pin                   |

| 12      | GND       | Ground Pin          | ※Internally shorted to the 11Pin                   |

| 13      | NC        | No Connection       |                                                    |

| 14      | Tab (GND) | Tab                 | ※Internally shorted to the GND                     |

| 15      | Tab (GND) | Tab                 | ※Internally shorted to the GND                     |

| 16      | SVD       | SENSE Voltage R     | eduction Detection Output Pin ("Low" at detection) |

| 17      | BVD       | Battery Voltage Re  | eduction Detection Output Pin ("Low" at detection) |

| 18      | NC        | No Connection       |                                                    |

| 19      | SENSE     | SENSE Pin           |                                                    |

| 20      | VOUT      | Voltage Regulator O | Dutput Pin                                         |

| 21      | Tab (GND) | Tab                 | ※Internally shorted to the GND                     |

| 22      | Tab (GND) | Tab                 | ※Internally shorted to the GND                     |

| 23      | NC        | No Connection       |                                                    |

| 24      | NC        | No Connection       |                                                    |

| 25      | NC        | No Connection       |                                                    |

| 26      | NC        | No Connection       |                                                    |

| 27      | NC        | No Connection       |                                                    |

| 28      | Tab (GND) | Tab                 | ※Internally shorted to the GND                     |

<sup>(1)</sup> The tab on the bottom of the package is substrate level (GND). It is recommended that the tab be connected to the ground plane on the board.

No.EA-501-220310

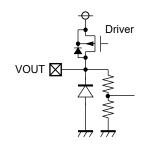

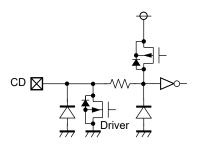

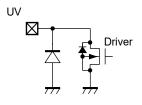

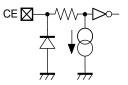

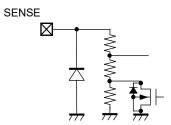

### PIN EQUIVALENT CIRCUIT DIAGRAMS

### < VOUT Pin >

### < SVD Pin >

< BVD Pin >

< SENSE Pin >

R5117x No.EA-501-220310

| Symbol           | Parameter                         | Rating                             | Unit     |

|------------------|-----------------------------------|------------------------------------|----------|

| M                | Input Voltage                     | -0.3 to 50                         | V        |

| Vin              | Peak Input Voltage <sup>(1)</sup> | 60                                 | V        |

| VCE              | CE Pin Input Voltage              | -0.3 to 50                         | V        |

| Vout             | Output Voltage                    | -0.3 to V <sub>IN</sub> + 0.3 ≤ 50 | V        |

| VSENSE           | SENSE Pin Voltage                 | -0.3 to 50                         | V        |

| V <sub>CD</sub>  | CD Pin Output Voltage             | -0.3 to 50                         | V        |

| V <sub>BVD</sub> | BVD Pin Output Voltage            | -0.3 to 7.0                        | V        |

| Vsvd             | SVD Pin Output Voltage            | -0.3 to 7.0                        | V        |

| PD               | Power Dissipation                 | Refer to Appendix "Power Diss      | ipation" |

| Tj               | Junction Temperature              | -40 to 125                         |          |

| Tstg             | Storage Temperature               | -55 to 125                         | °C       |

# **ABSOLUTE MAXIMUM RATINGS**

### ABSOLUTE MAXIMUM RATINGS

Electronic and mechanical stress momentarily exceeded absolute maximum ratings may cause permanent damage and may degrade the lifetime and safety for both device and system using the device in the field. The functional operation at or over these absolute maximum ratings are not assured.

# **RECOMMENDED OPERATING CONDITIONS**

| Symbol           | Parameter               | Rating     | Unit |

|------------------|-------------------------|------------|------|

| Vin              | Input Voltage           | 3.5 to 42  | V    |

| VCE              | CE Pin Input Voltage    | 0 to 42    | V    |

| VSENSE           | SENSE Pin Input Voltage | 0 to 6.0   | V    |

| V <sub>BVD</sub> | BVD Pin Output Voltage  | 0 to 6.0   | V    |

| V <sub>SVD</sub> | SVD Pin Output Voltage  | 0 to 6.0   | V    |

| Та               | Operating Temperature   | -40 to 105 | °C   |

### RECOMMENDED OPERATING CONDITIONS

All of electronic equipment should be designed that the mounted semiconductor devices operate within the recommended operating conditions. The semiconductor devices cannot operate normally over the recommended operating conditions, even if they are used over such conditions by momentary electronic noise or surge. And the semiconductor devices may receive serious damage when they continue to operate over the recommended operating conditions.

<sup>(1)</sup> Duration time: 200 ms

# **ELECTRICAL CHARACTERISTICS**

$C_{\text{IN}}$  = 1.0  $\mu F,\,C_{\text{OUT}}$  = 10  $\mu F,\,V_{\text{IN}}$  = 14 V, unless otherwise noted.

The specifications surrounded by  $\square$  are guaranteed by design engineering at  $-40^{\circ}C \le Ta \le 105^{\circ}C$ .

### R5117xxxx

| For All            |                                                            |                                                                    |                                |      |      | (T   | a = 25°C) |

|--------------------|------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------|------|------|------|-----------|

| Symbol             | Parameter                                                  | Co                                                                 | ondition                       | Min. | Тур. | Max. | Unit      |

| Iss Supply Current | $\mathbf{L}_{\mathbf{r}} = 0  \mathbf{m}  \mathbf{A}  (1)$ | $3.5V \le V_{BVSET} < 8.0V$                                        |                                | 35   | 65   |      |           |

|                    |                                                            | $I_{OUT} = 0 \text{ mA}^{(1)}$<br>8.0V $\leq V_{BVSET} \leq 12.0V$ | $8.0V \le V_{BVSET} \le 12.0V$ |      | - 35 | 60   | μA        |

| Istandby           | Standby Current                                            | $V_{IN} = 14 V, V_{CE} =$                                          |                                | 10   | 25   | μA   |           |

| I <sub>PD</sub>    | CE Pull-down Current                                       |                                                                    |                                |      | 0.2  | 0.6  | μA        |

| VCEH               | CE Input Voltage, high                                     |                                                                    |                                | 2.0  |      | 42   | V         |

| V <sub>CEL</sub>   | CE Input Voltage, low                                      |                                                                    |                                | 0    |      | 1.0  | V         |

All test items listed under Electrical Characteristics are done under the pulse load condition (Tj ≈ Ta = 25°C).

| VR Secti         | on                                      |                                         |                                                             |         |      | (Ta     | = 25°C) |

|------------------|-----------------------------------------|-----------------------------------------|-------------------------------------------------------------|---------|------|---------|---------|

| Symbol           | Parameter                               | Co                                      | ondition                                                    | Min.    | Тур. | Max.    | Unit    |

| Maria            | Output Voltage                          | V <sub>IN</sub> = 14 V,                 | Ta = 25°C                                                   | ×0.995  |      | ×1.005  | V       |

| VOUT             | Vout Output Voltage                     | I <sub>OUT</sub> = 1 mA                 | -40°C ≤ Ta ≤ 105°C                                          | ×0.9875 |      | ×1.0075 | V       |

| ΔVουτ/           | Lood Doculation                         | <u> </u>                                | 1 mA ≤ I <sub>OUT</sub> ≤ 300 mA                            | -10     | 0    | 10      |         |

| $\Delta I_{OUT}$ | Load Regulation                         | $V_{\rm IN} = V_{\rm SET} + 3.0  \rm V$ | 1 mA ≤ I <sub>OUT</sub> ≤ 500 mA                            | -15     | 0    | 15      | mV      |

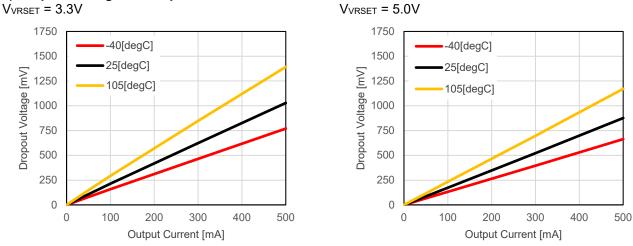

| VDIF             | Dropout Voltage                         | Ιουτ <b>= 500 mA</b>                    | V <sub>SET</sub> = 3.3 V                                    |         | 1.1  | 1.7     | V       |

| • Dii            |                                         |                                         | V <sub>SET</sub> = 5.0 V                                    |         | 0.9  | 1.5     | •       |

| ΔVout/           | Line Regulation                         | Ιουτ = 1 mA                             | $8.0 \text{ V} \leq \text{V}_{\text{IN}} \leq 16 \text{ V}$ | -10     | 0    | 10      | mV      |

| $\Delta V_{IN}$  |                                         | 1001 - 1  IIIA                          | $6.0 \text{ V} \leq \text{V}_{\text{IN}} \leq 32 \text{ V}$ | -25     | 0    | 25      | IIIV    |

| ILIM             | Output Current Limit                    | V <sub>IN</sub> = 8.0 V                 |                                                             | 500     | 750  |         | mA      |

| Isc              | Short Current Limit                     | V <sub>OUT</sub> = 0 V                  | 70                                                          | 105     | 150  | mA      |         |

| TTSD             | Thermal Shutdown<br>Temperature         | Junction Tempera                        | 165                                                         | 175     |      | °C      |         |

| T <sub>TSR</sub> | Thermal Shutdown<br>Release Temperature | Junction Tempera                        | ture                                                        | 125     | 145  |         | °C      |

All test items listed under Electrical Characteristics are done under the pulse load condition (Tj  $\approx$  Ta = 25°C).

<sup>&</sup>lt;sup>(1)</sup> Supply current, Standby current are depending on VDD Voltage and battery voltage detector setting when the detector power is turned on all the time. Refer to the Supply Current data in TYPICAL CHARACTERISTICS for detail information.

# **ELECTRICAL CHARACTERISTICS**

$C_{IN}$  = 1.0 µF,  $C_{OUT}$  = 10 µF,  $V_{IN}$  = 14 V, unless otherwise noted.

The specifications surrounded by  $\square$  are guaranteed by design engineering at  $-40^{\circ}C \le Ta \le 105^{\circ}C$ .

### SVD / BVD Sacti

|                | D Sections                                           | <b>_</b>                                       |                              |                                                                |                              | a = 25°C) |

|----------------|------------------------------------------------------|------------------------------------------------|------------------------------|----------------------------------------------------------------|------------------------------|-----------|

| Symbol         | Parameter                                            | Condition                                      | Min.                         | Тур.                                                           | Max.                         | Unit      |

| \/             | Battery Voltage Detector                             | Ta = 25°C                                      | ×0.992                       |                                                                | ×1.008                       | V         |

| VBVDET         | Threshold                                            | −40°C ≤ Ta ≤ 105°C                             | ×0.98                        |                                                                | ×1.01                        | V         |

| VSVDET         | SENSE Voltage Detector                               | Ta = 25°C                                      | ×0.995                       |                                                                | ×1.005                       | V         |

| VSVDET         | Threshold                                            | −40°C ≤ Ta ≤ 105°C                             | ×0.9875                      |                                                                | ×1.0075                      | v         |

| VBVHYS         | Battery Voltage<br>Threshold Hysteresis              |                                                | V <sub>BVDET</sub><br>×0.01  | $\begin{array}{c} V_{\text{BVDET}} \\ \times 0.03 \end{array}$ | V <sub>BVDET</sub><br>×0.05  | V         |

| Vsvhys         | SENSE Voltage Detector<br>Threshold Hysteresis       |                                                | V <sub>SVDET</sub><br>×0.003 | V <sub>SVDET</sub><br>×0.005                                   | V <sub>SVDET</sub><br>×0.007 | V         |

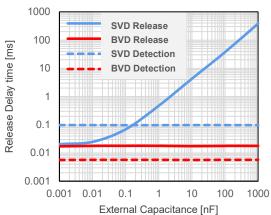

| <b>t</b> DELAY | Release Output Delay<br>Time (Power-on Reset)        | $C_{D} = 10 \text{ nF}^{(1)}$                  | 2                            | 4                                                              | 8                            | ms        |

| Vuvlo          | UVLO Detector<br>Threshold                           |                                                |                              | 1.8                                                            | 2.8                          | V         |

| VUVLOHYS       | UVLO Detector<br>Threshold Hysteresis                |                                                |                              | 0.1                                                            | 0.2                          | V         |

| VBVD           | BVD Pull-up Voltage                                  |                                                |                              |                                                                | 6.0                          | V         |

| Vsvd           | SVD Pull-up Voltage                                  |                                                |                              |                                                                | 6.0                          | V         |

| IOUTBVD        | Nch Output Current<br>(BVD Output Pin)               | $V_{IN} = V_{BVDET} - 0.1V, V_{DS} = 0.1V$     | 0.8                          | 2.0                                                            |                              | mA        |

| IOUTSVD        | Nch Output Current<br>(SVD Output Pin)               | $V_{IN}$ = 3.0 V, $V_{DS}$ = 0.1 V             | 0.8                          | 2.0                                                            |                              | mA        |

| ILEAKBVD       | Nch Leakage Current<br>(BVD Output Pin)              | V <sub>BVD</sub> = 5.5 V                       |                              |                                                                | 0.3                          | μΑ        |

| ILEAKSVD       | Nch Leakage Current<br>(SVD Output Pin)              | V <sub>SVD</sub> = 5.5 V                       |                              |                                                                | 0.3                          | μΑ        |

| RLCD           | C <sub>D</sub> Pin Discharge<br>Nch Tr.ON Resistance | V <sub>CE</sub> = 0 V, V <sub>CD</sub> = 0.1 V |                              | 1.2                                                            | 3.0                          | kΩ        |

All test items listed under Electrical Characteristics are done under the pulse load condition (Tj ≈ Ta = 25°C).

<sup>&</sup>lt;sup>(1)</sup> t<sub>DELAY</sub> is adjustable by only C<sub>D</sub> of SENSE Voltage Detector. t<sub>DELAY</sub> of Battery Voltage Detector is fixed internally. Refer to Release delay time data in TYPICAL CHARACTERISTICS for detail information.

No.EA-501-220310

### **R5117x Product-specific Electrical Characteristics**

The specifications surrounded by  $\square$  are guaranteed by design engineering at  $-40^{\circ}C \le Ta \le 105^{\circ}C$

|              |       | Vout    |       | Vout               |       |       |  |

|--------------|-------|---------|-------|--------------------|-------|-------|--|

| Product Name |       | Ta=25°C |       | -40°C ≤ Ta ≤ 105°C |       |       |  |

|              | Min.  | Тур.    | Max.  | Min.               | Тур.  | Max.  |  |

| R5117x001A   | 4.975 | 5.000   | 5.025 | 4.938              | 5.000 | 5.037 |  |

| R5117x002A   | 3.284 | 3.300   | 3.316 | 3.259              | 3.300 | 3.324 |  |

| Product Name | V <sub>BVDET</sub><br>Ta=25°C |       |       | V <sub>BVDET</sub><br>-40°C ≤ Ta ≤ 105°C |       |       |         |                          |         |  |

|--------------|-------------------------------|-------|-------|------------------------------------------|-------|-------|---------|--------------------------|---------|--|

| Froduct Name | Min.                          | Тур.  | Max.  | Min.                                     | Typ.  | Max.  | Min.    | Ta=25°C<br>Min. Typ. Max |         |  |

| R5117x001A   | 6.647                         | 6.700 | 6.753 | 6.566                                    | 6.700 | 6.767 | 0.06700 | 0.20100                  | 0.33500 |  |

| R5117x002A   | 5.159                         | 5.200 | 5.241 | 5.096                                    | 5.200 | 5.252 | 0.05200 | 0.15600                  | 0.26000 |  |

| V <sub>SVDET</sub> |       |         |       |       |                            |       | V <sub>SVHYS</sub> |         |         |  |

|--------------------|-------|---------|-------|-------|----------------------------|-------|--------------------|---------|---------|--|

| Product Name       |       | Ta=25°C |       | -40°C | -40°C ≤ Ta ≤ 105°C Ta=25°C |       |                    |         |         |  |

|                    | Min.  | Тур.    | Max.  | Min.  | Тур.                       | Max.  | Min.               | Тур.    | Max.    |  |

| R5117x001A         | 4.796 | 4.820   | 4.844 | 4.760 | 4.820                      | 4.856 | 0.01446            | 0.02410 | 0.03374 |  |

| R5117x002A         | 3.165 | 3.180   | 3.195 | 3.141 | 3.180                      | 3.203 | 0.00954            | 0.01590 | 0.02226 |  |

# THEORY OF OPERATION

### **Thermal Shutdown**

When the junction temperature of this device exceeds 175°C (Typ.), the built-in thermal shutdown circuit stops the regulator operation. After that, when the temperature drops to 145°C (Typ.) or lower, the regulator restarts the operation. Unless eliminating the overheating problem, the regulator turns on and off repeatedly and a pulse shaped output voltage occurs as result.

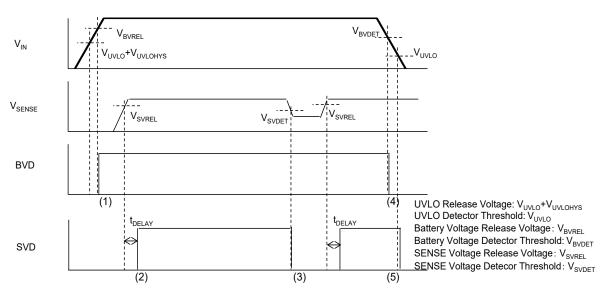

### R5117xxx Voltage Detector

R5117xxx Voltage Detector Timing Chart

- When the Input pin voltage (V<sub>IN</sub>) exceed the Battery voltage release voltage (V<sub>BVREL</sub>), the BVD pin output becomes "High" after the release delay time (Typ. 20µs).

- (2) When SENSE pin voltage (V<sub>SENSE</sub>) exceed the SENSE voltage release voltage (V<sub>SVREL</sub>), the SVD pin output becomes "High" after the release delay time (t<sub>DELAY</sub>).

- (3) When V<sub>SENSE</sub> decreases less than the SENSE voltage detector threshold (V<sub>SVDET</sub>), the SVD pin output becomes "Low" after the detection delay time (Typ.100 μs) and enters the SENSE voltage detecting state.

- (4) When the Input pin voltage (V<sub>IN</sub>) decreases less than the Battery voltage detector threshold (V<sub>BVDET</sub>), the BVD pin output becomes "Low" after the detection delay time (Typ.6.0µs) and enters the Battery voltage detecting state.

- (5) When the Input pin voltage (V<sub>IN</sub>) decreases less than the UVLO detector threshold (V<sub>UVLO</sub>), the SVD pin output becomes "Low".

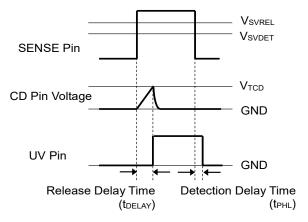

# SENSE Voltage Monitoring VD Delay Operation and Release Delay Time (t<sub>DELAY</sub>)

### At SENSE Voltage Detection

When supplying a voltage higher than the SENSE voltage release voltage ( $V_{SVREL}$ ) to the SENSE pin, a charging to an external capacitor starts and the CD pin voltage ( $V_{CD}$ ) increases. The SVD pin voltage ( $V_{SVD}$ ) maintains "Low" until  $V_{CD}$  reaches the CD pin threshold voltage ( $V_{TCD}$ ). When  $V_{CD}$  exceeds  $V_{TCD}$ ,  $V_{SVD}$  is inverted from "Low" to "High". The release delay time ( $t_{DELAY}$ ) is the period from the time the SENSE pin voltage ( $V_{SENSE}$ ) exceeds  $V_{SVREL}$  to a rising edge of  $V_{SVD}$ . When the output voltage turns from "Low" to "High", a charge carrier of the external capacitor starts discharging. When supplying a voltage lower than the SENSE voltage detector threshold ( $V_{SVDET}$ ) to the SENSE pin, the detection delay time ( $t_{PHL}$ ) remains constant independently of the external capacitor.  $t_{PHL}$  is the period that  $V_{SVD}$  is inverted from "High" to "Low".

SENSE Voltage Release Delay Timing Diagram

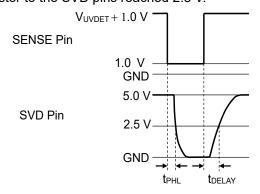

### Calculation of SENSE Voltage Release Delay Time

The following equation can calculate a typical value of the release delay time ( $t_{DELAY}$ ) with using the external capacitor ( $C_D$ ).

$t_{\text{DELAY}}(s) = 0.72 \times C_{\text{D}}(\text{F}) / (1.8 \times 10^{-6})$

$t_{DELAY}$  is the period from supplying a pulse voltage of "1.0 V to (V<sub>SVDET</sub>) + 1.0 V" to the SENSE pin by pulling-up SVD pin to 5 V with 100 k $\Omega$  resistor to the SVD pins reached 2.5 V.

### Voltage Setting of Voltage Regulator

The SENSE Voltage Detector (SVD) detects the drop and rise of the Voltage Regulator (VR). When the SENSE release voltage is set to a voltage above the VR output voltage, the reset signal of SVD is not released even if SVD monitors the VR output voltage returns to the normal value after detecting the drop of VR. To prevent this issue, the following conditions are required between Vout and V<sub>SVREL</sub>,

(VR Set Output Voltage) x 0.9875 - 15 mV\* > (SENSE Set Detector Threshold) x 1.0075 x 1.007 \*15mV is the worst value of load regulation

When using a device without the above conditions of  $V_{OUT}$  and  $V_{SVDET}$ , careful consideration must be given to the system operation before use.

# **APPLICATION INFORMATION**

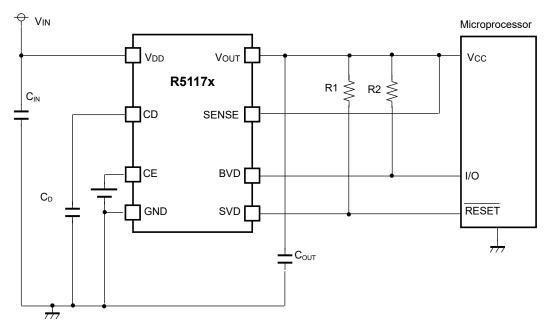

### TYPICAL APPLICATIONS

### **R5117xxx TYPICAL APPLICATIONS**

### **Recommended Components**

| Symbol | Description                                                                                                                                                                                                       |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CIN    | Ceramic Capacitor, 1.0 $\mu$ F or more, 50V Rated Voltage, CGA4J3X7R1H105K, TDK                                                                                                                                   |

| Соит   | Ceramic Capacitor, 10 µF or more, 50V Rated Voltage, CGA4J1X7R0J106K, TDK                                                                                                                                         |

| CD     | A capacitor corresponding to setting of Release Output Delay Time                                                                                                                                                 |

| R1/R2  | A resistor covering the output current at Nch. driver ON and the leakage current at Nch. driver OFF. Refer to "Electrical Characteristic" providing the evaluation result with using a resistor of $100k\Omega$ . |

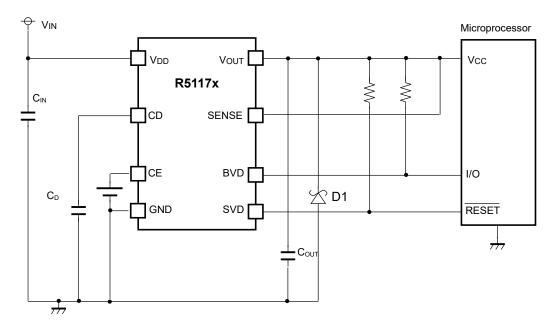

### TYPICAL APPLICATION FOR IC CHIP BREAKDOWN PREVENTION

When a sudden surge of electrical current travels along the VOUT pin and GND due to a short-circuit, electrical resonance of a circuit involving an output capacitor ( $C_{OUT}$ ) and a short circuit inductor generates a negative voltage and may damage the device or the load devices. Connecting a schottky diode (D1) between the VOUT pin and GND has the effect of preventing damage to them.

# **TECHNICAL NOTES**

The performance of a power source circuit using this device is highly dependent on a peripheral circuit. A peripheral component or the device mounted on PCB should not exceed a rated voltage, a rated current or a rated power. When designing a peripheral circuit, please be fully aware of the following points.

### Phase Compensation

Phase compensation is provided to secure stable operation even when the load current is varied by utilizing capacity of the output ceramic capacitor and Equivalent Series Resistance (ESR). For this purpose, be sure to use a capacitor with 10  $\mu$ F or more (C<sub>OUT</sub>) and wire it to the pin as short as possible.

Evaluate the circuit with consideration of temperature and frequency characteristics, in case ESR value of the capacitor is large and the output is unstable. The capacitor with 1.0  $\mu$ F or more (C<sub>IN</sub>) connected in between VDD pin and GND pin must be wired the shortest.

**R5117x** No.EA-501-220310

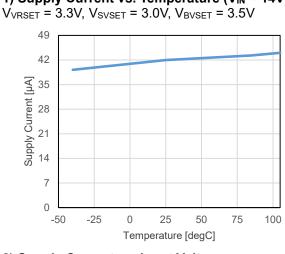

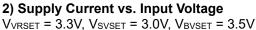

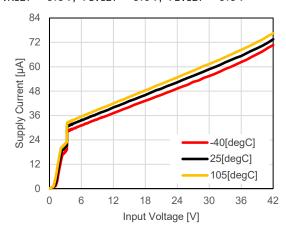

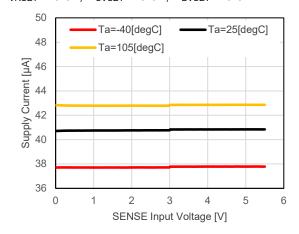

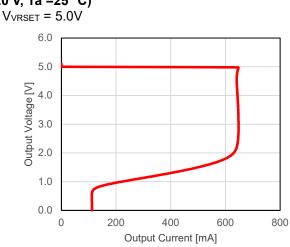

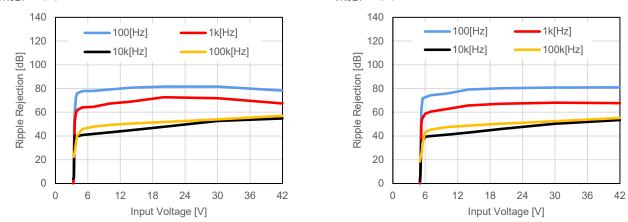

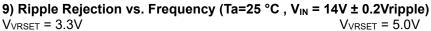

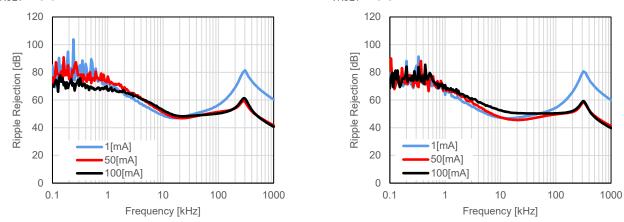

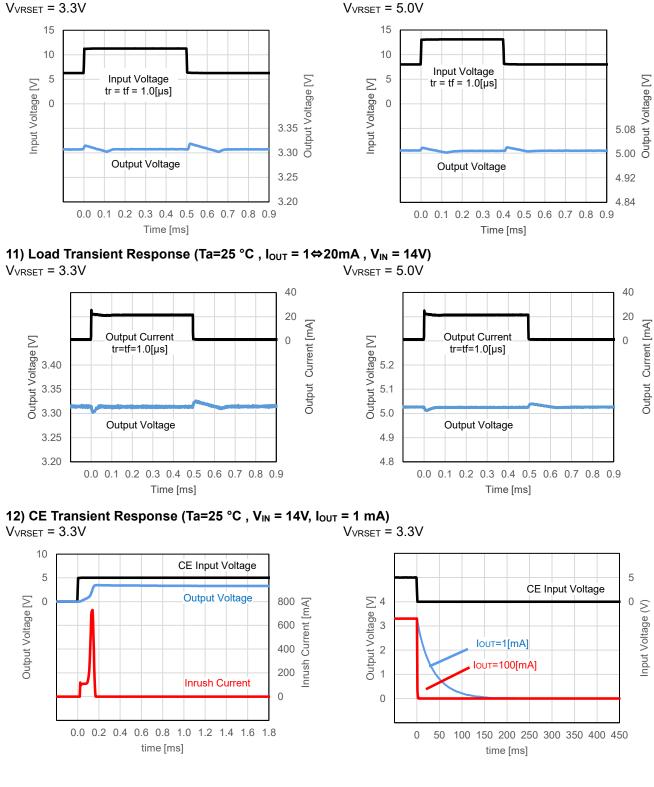

### TYPICAL CHARACTERISTICS

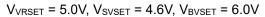

Note: Typical Characteristics are intended to be used as reference data; they are not guaranteed. **1) Supply Current vs. Temperature (V\_{IN} = 14V)**   $V_{VRSET} = 3.3V$ ,  $V_{SVSET} = 3.0V$ ,  $V_{BVSET} = 3.5V$  $V_{VRSET} = 5.0V$ ,  $V_{SVSET} = 4.6V$ ,  $V_{BVSET} = 6.0V$

**3) Supply Current vs. SENSE Voltage** VVRSET = 3.3V, VSVSET = 3.0V, VBVSET = 3.5V

42 35 Supply Current [µA] 28 21 14 7 0 -25 25 50 75 100 -50 0 Temperature [degC]

VVRSET = 5.0V, VSVSET = 4.6V, VBVSET = 6.0V

No.EA-501-220310

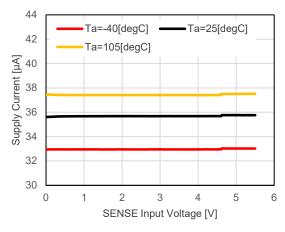

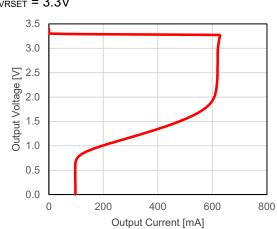

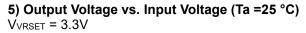

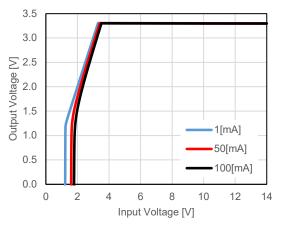

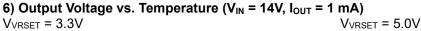

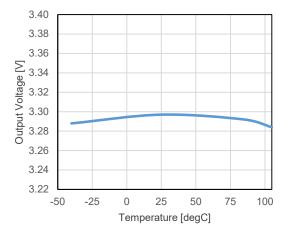

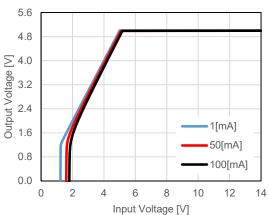

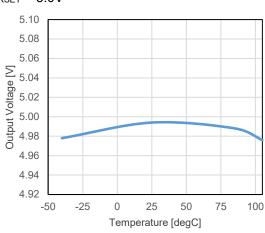

#### 4) Output Voltage vs. Output Current (V<sub>IN</sub> = V<sub>VRSET</sub> + 3.0 V, Ta =25 °C) V<sub>VRSET</sub> = 3.3V V<sub>VRSET</sub> = 5.0V

No.EA-501-220310

7) Dropout Voltage vs. Output Current

No.EA-501-220310

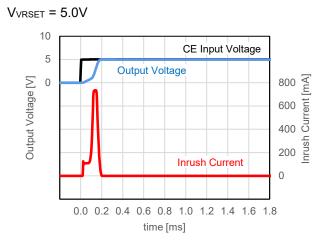

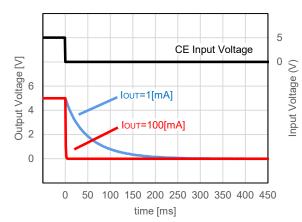

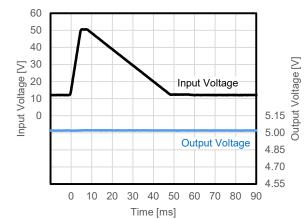

### 10) Input Transient Response (Ta=25 °C , V<sub>IN</sub> = V<sub>VRSET</sub> + 3.0 V ⇔ V<sub>VRSET</sub> + 8.0 V, I<sub>OUT</sub> = 1 mA)

No.EA-501-220310

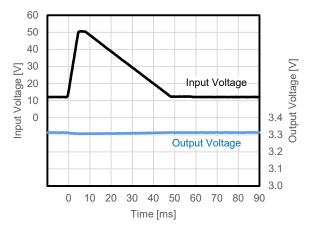

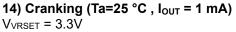

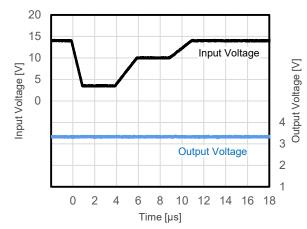

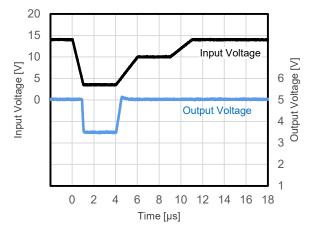

13) Load Dump (Ta=25 °C ,  $I_{OUT}$  = 1 mA) VVRSET = 3.3V

$V_{VRSET} = 5.0V$

No.EA-501-220310

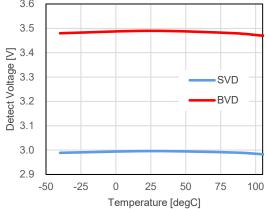

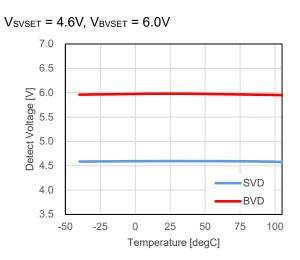

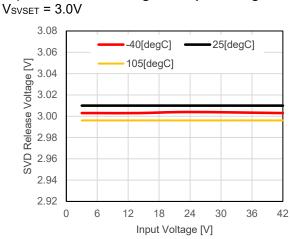

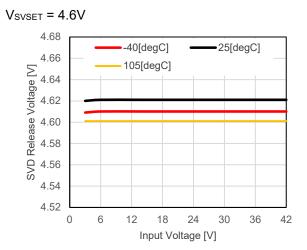

### 15) SVD/BVD Detection Voltage vs. Temperature

VSVSET = 3.0V, VBVSET = 3.5V

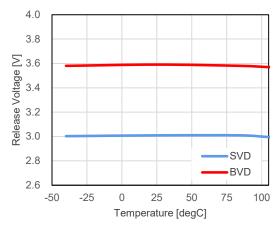

16) SVD/BVD Release Voltage vs. Temperature  $V_{SVSET}$  = 3.0V,  $V_{BVSET}$  = 3.5V

**17) SVD Detection Voltage vs. Input Voltage** V<sub>SVSET</sub> = 3.0V

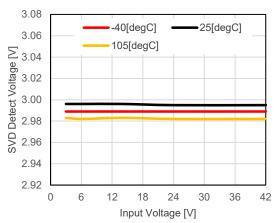

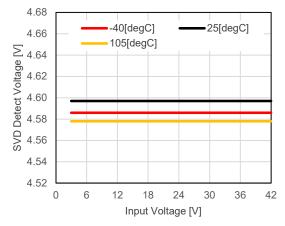

$V_{\text{SVSET}} = 4.6V, V_{\text{BVSET}} = 6.0V$

No.EA-501-220310

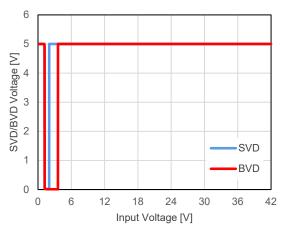

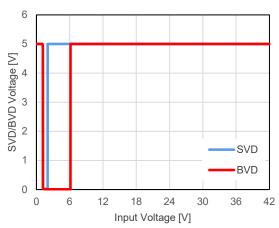

**19)** SVD/BVD Voltage vs. Input Voltage (Ta =25 °C) V<sub>SVSET</sub> = 3.0V, V<sub>BVSET</sub> = 3.5V, Pull-up Voltage = 5.0V

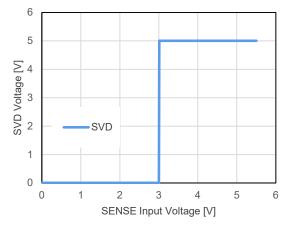

20) SVD Voltage vs. SENSE Voltage (Ta =25 °C) V<sub>SVSET</sub> = 3.0V, Pull-up Voltage = 5.0V

VSVSET = 4.6V, VBVSET = 6.0V, Pull-up Voltage = 5.0V

No.EA-501-220310

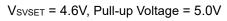

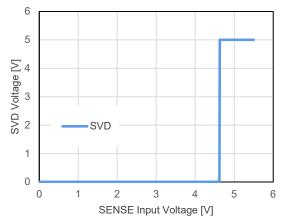

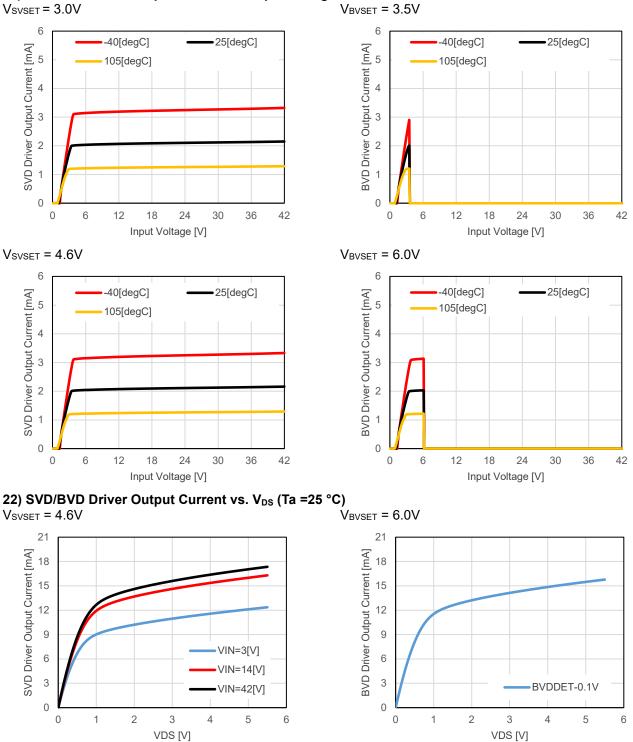

### 21) SVD/BVD Driver Output Current vs. Input Voltage

V<sub>SVSET</sub> = 3.0V

No.EA-501-220310

$V_{\text{SVSET}} = 4.6V, V_{\text{BVSET}} = 6.0V$

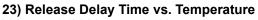

**24) Detection Delay Time vs. Temperature** V<sub>SVSET</sub> = 4.6V, V<sub>BVSET</sub> = 6.0V

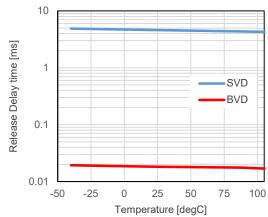

**25) Release Delay Time vs. Input Voltage** V<sub>SVSET</sub> = 4.6V

No.EA-501-220310

```

26) Detection/Release Delay Time vs. External Capacitance for CD Pin (Ta =25 °C)

V_{\text{SVSET}} = 4.6V, V_{\text{BVSET}} = 6.0V

```

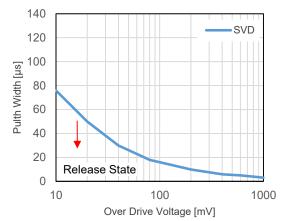

27) SENSE Pulse Width vs. SENSE Overdrive Voltage (Ta =25 °C)

Limit Pulse of Release State

$V_{SVSET} = 4.6V$

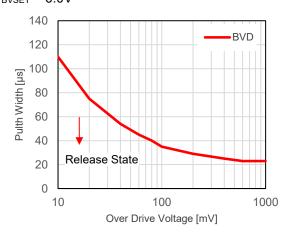

28) V<sub>IN</sub> Pulse Width vs. V<sub>IN</sub> Overdrive Voltage (Ta =25 °C) Limit Pulse of Release State  $V_{BVSET} = 6.0V$

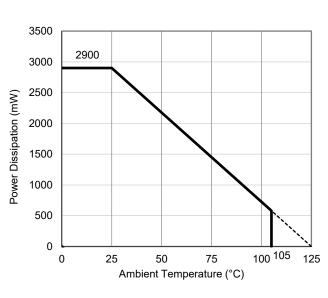

# POWER DISSIPATION

# **HSOP-8E**

PD-HSOP-8E-(105125)-JE-A

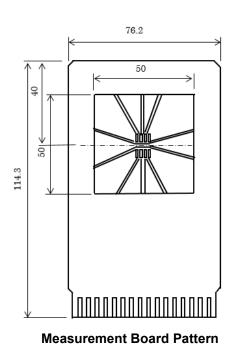

The power dissipation of the package is dependent on PCB material, layout, and environmental conditions. The following measurement conditions are based on JEDEC STD. 51-7.

#### **Measurement Conditions**

| ltem             | Measurement Conditions                                                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Environment      | Mounting on Board (Wind Velocity = 0 m/s)                                                                                                                                                    |

| Board Material   | Glass Cloth Epoxy Plastic (Four-Layer Board)                                                                                                                                                 |

| Board Dimensions | 76.2 mm × 114.3 mm × 0.8 mm                                                                                                                                                                  |

| Copper Ratio     | Outer Layer (First Layer): Less than 95% of 50 mm Square<br>Inner Layers (Second and Third Layers): Approx. 100% of 50 mm Square<br>Outer Layer (Fourth Layer): Approx. 100% of 50 mm Square |

| Through-holes    | φ 0.3 mm × 21 pcs                                                                                                                                                                            |

#### **Measurement Result**

(Ta = 25°C, Tjmax = 125°C)

| Item                                     | Measurement Result |

|------------------------------------------|--------------------|

| Power Dissipation                        | 2900 mW            |

| Thermal Resistance (θja)                 | θja = 34.5°C/W     |

| Thermal Characterization Parameter (ψjt) | ψjt = 10°C/W       |

$\theta$ ja: Junction-to-ambient thermal resistance.

wjt: Junction-to-top of package thermal characterization parameter

Power Dissipation vs. Ambient Temperature

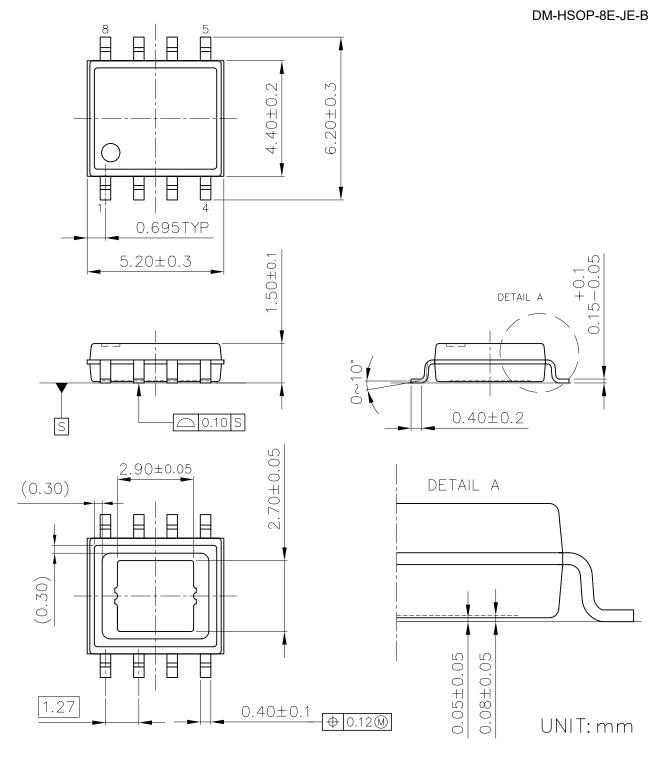

# PACKAGE DIMENSIONS

# HSOP-8E

HSOP-8E Package Dimensions

Nisshinbo Micro Devices Inc.

i

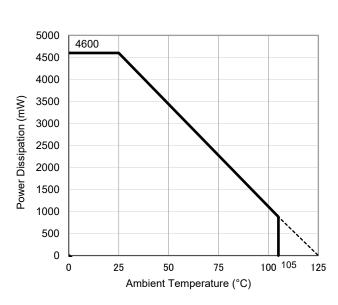

# POWER DISSIPATION

# HQFN0808-28

PD-HQFN0808-28-(105125)-JE-A

The power dissipation of the package is dependent on PCB material, layout, and environmental conditions. The following measurement conditions are based on JEDEC STD. 51-7.

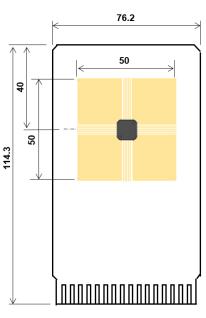

### **Measurement Conditions**

| ltem             | Measurement Conditions                                                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Environment      | Mounting on Board (Wind Velocity = 0 m/s)                                                                                                                                                    |

| Board Material   | Glass Cloth Epoxy Plastic (Four-Layer Board)                                                                                                                                                 |

| Board Dimensions | 76.2 mm × 114.3 mm × 0.8 mm                                                                                                                                                                  |

| Copper Ratio     | Outer Layer (First Layer): Less than 95% of 50 mm Square<br>Inner Layers (Second and Third Layers): Approx. 100% of 50 mm Square<br>Outer Layer (Fourth Layer): Approx. 100% of 50 mm Square |

| Through-holes    | φ 0.3 mm × 72 pcs                                                                                                                                                                            |

#### **Measurement Result**

(Ta = 25°C, Tjmax = 125°C) Item **Measurement Result** 4600 mW **Power Dissipation** Thermal Resistance (θja) θja = 21.5°C/W Thermal Characterization Parameter (ψjt)  $\psi jt = 5^{\circ}C/W$

θja: Junction-to-ambient thermal resistance.

wjt: Junction-to-top of package thermal characterization parameter

**Power Dissipation vs. Ambient Temperature**

**Measurement Board Pattern**

# PACKAGE DIMENSIONS

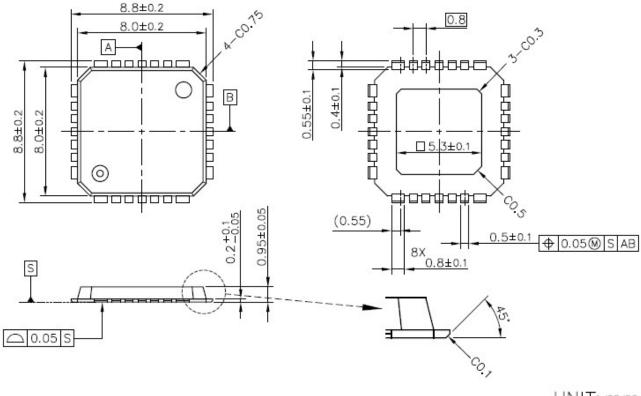

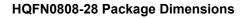

# HQFN0808-28

DM-HQFN0808-28-JE-A

UNIT: mm

- 1. The products and the product specifications described in this document are subject to change or discontinuation of production without notice for reasons such as improvement. Therefore, before deciding to use the products, please refer to our sales representatives for the latest information thereon.

- 2. The materials in this document may not be copied or otherwise reproduced in whole or in part without the prior written consent of us.

- 3. This product and any technical information relating thereto are subject to complementary export controls (so-called KNOW controls) under the Foreign Exchange and Foreign Trade Law, and related politics ministerial ordinance of the law. (Note that the complementary export controls are inapplicable to any application-specific products, except rockets and pilotless aircraft, that are insusceptible to design or program changes.) Accordingly, when exporting or carrying abroad this product, follow the Foreign Exchange and Foreign Trade Control Law and its related regulations with respect to the complementary export controls.

- 4. The technical information described in this document shows typical characteristics and example application circuits for the products. The release of such information is not to be construed as a warranty of or a grant of license under our or any third party's intellectual property rights or any other rights.

- 5. The products listed in this document are intended and designed for use as general electronic components in standard applications (office equipment, telecommunication equipment, measuring instruments, consumer electronic products, amusement equipment etc.). Those customers intending to use a product in an application requiring extreme quality and reliability, for example, in a highly specific application where the failure or misoperation of the product could result in human injury or death should first contact us.

- Aerospace Equipment

- Equipment Used in the Deep Sea

- Power Generator Control Equipment (nuclear, steam, hydraulic, etc.)

- Life Maintenance Medical Equipment

- Fire Alarms / Intruder Detectors

- Vehicle Control Equipment (automotive, airplane, railroad, ship, etc.)

- Various Safety Devices

- Traffic control system

- Combustion equipment

In case your company desires to use this product for any applications other than general electronic equipment mentioned above, make sure to contact our company in advance. Note that the important requirements mentioned in this section are not applicable to cases where operation requirements such as application conditions are confirmed by our company in writing after consultation with your company.

- 6. We are making our continuous effort to improve the quality and reliability of our products, but semiconductor products are likely to fail with certain probability. In order to prevent any injury to persons or damages to property resulting from such failure, customers should be careful enough to incorporate safety measures in their design, such as redundancy feature, fire containment feature and fail-safe feature. We do not assume any liability or responsibility for any loss or damage arising from misuse or inappropriate use of the products.

- 7. The products have been designed and tested to function within controlled environmental conditions. Do not use products under conditions that deviate from methods or applications specified in this datasheet. Failure to employ the products in the proper applications can lead to deterioration, destruction or failure of the products. We shall not be responsible for any bodily injury, fires or accident, property damage or any consequential damages resulting from misuse or misapplication of the products.

- 8. Quality Warranty

- 8-1. Quality Warranty Period

In the case of a product purchased through an authorized distributor or directly from us, the warranty period for this product shall be one (1) year after delivery to your company. For defective products that occurred during this period, we will take the quality warranty measures described in section 8-2. However, if there is an agreement on the warranty period in the basic transaction agreement, quality assurance agreement, delivery specifications, etc., it shall be followed.

8-2. Quality Warranty Remedies

When it has been proved defective due to manufacturing factors as a result of defect analysis by us, we will either deliver a substitute for the defective product or refund the purchase price of the defective product.

- Note that such delivery or refund is sole and exclusive remedies to your company for the defective product.

- 8-3. Remedies after Quality Warranty Period

With respect to any defect of this product found after the quality warranty period, the defect will be analyzed by us. On the basis of the defect analysis results, the scope and amounts of damage shall be determined by mutual agreement of both parties. Then we will deal with upper limit in Section 8-2. This provision is not intended to limit any legal rights of your company.

- 9. Anti-radiation design is not implemented in the products described in this document.

- 10. The X-ray exposure can influence functions and characteristics of the products. Confirm the product functions and characteristics in the evaluation stage.

- 11. WLCSP products should be used in light shielded environments. The light exposure can influence functions and characteristics of the products under operation or storage.

- 12. Warning for handling Gallium and Arsenic (GaAs) products (Applying to GaAs MMIC, Photo Reflector). These products use Gallium (Ga) and Arsenic (As) which are specified as poisonous chemicals by law. For the prevention of a hazard, do not burn, destroy, or process chemically to make them as gas or power. When the product is disposed of, please follow the related regulation and do not mix this with general industrial waste or household waste.

- 13. Please contact our sales representatives should you have any questions or comments concerning the products or the technical information.

Nisshinbo Micro Devices Inc.

Official website https://www.nisshinbo-microdevices.co.jp/en/ Purchase information https://www.nisshinbo-microdevices.co.jp/en/buy/