#### **General Description**

These N-Channel enhancement mode power field effect transistors are using trench DMOS technology. This advanced technology has been especially tailored to minimize on-state resistance, provide superior switching performance, and withstand high energy pulse in the avalanche and commutation mode. These devices are well suited for high efficiency fast switching applications.

| BV <sub>DSS</sub> | R <sub>DS(ON)</sub> | I <sub>D</sub> |

|-------------------|---------------------|----------------|

| 30V               | 5.1 mΩ              | 48 A           |

#### **Features**

- $R_{DS(ON)} \leq \overline{5.1m\Omega} \overline{@V_{GS}} = \overline{10V}$

- · Improved dv/dt Capability

- Fast Switching

- · Green Device Available

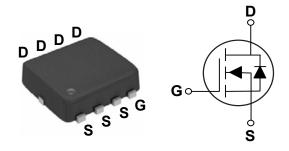

#### PPAK3X3 Pin Configuration

#### **Applications**

- · MB / VGA / Vcore

- POL Applications

- SMPS 2<sup>nd</sup> SR

| Symbol          | Parameter                                         | Rating     | Units |

|-----------------|---------------------------------------------------|------------|-------|

| $V_{DS}$        | Drain-Source Voltage                              | 30         | V     |

| $V_{GS}$        | Gate-Source Voltage                               | ±20        | V     |

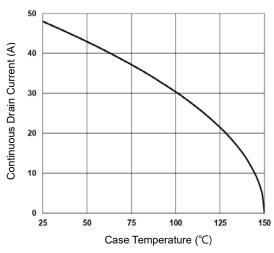

| I <sub>D</sub>  | Drain Current - Continuous                        | 48         | Α     |

| I <sub>DM</sub> | Drain Current - Pulsed                            | 100        | Α     |

| EAS             | Single Pulse Avalanche Energy (NOTE 1)            | 31.25      | mJ    |

| IAS             | Single Pulse Avalanche Current (NOTE 1)           | 25         | Α     |

| $P_D$           | Power Dissipation (T <sub>C</sub> =25°C) (NOTE 2) | 17.4       | W     |

| $T_J$           | Operating Junction Temperature                    | 150        | °C    |

| $T_{STG}$       | Storage Temperature Range                         | -50 to 150 | °C    |

| larking Code    |                                                   | NC5P1      |       |

| Thermal Characteristics |                                        |        |      |  |  |

|-------------------------|----------------------------------------|--------|------|--|--|

| Symbol                  | Parameter                              | Rating | Unit |  |  |

| $R_{\theta JA}$         | Thermal Resistance Junction to Ambient | 50     | °C/W |  |  |

| $R_{	heta JC}$          | Thermal Resistance Junction to Case    | 7.2    | °C/W |  |  |

### Electrical Characteristics (T<sub>J</sub>=25°C, unless otherwise noted)

#### **Off Characteristics**

| Symbol            | Parameter                      | Conditions                    | Min. | Тур. | Max. | Unit |

|-------------------|--------------------------------|-------------------------------|------|------|------|------|

| BV <sub>DSS</sub> | Drain-Source Breakdown Voltage | $V_{GS}$ =0V , $I_D$ =250uA   | 30   |      |      | V    |

| I <sub>DSS</sub>  | Drain-Source Leakage Current   | $V_{DS}$ =24V , $V_{GS}$ =0V  |      |      | 1    | uA   |

| I <sub>GSS</sub>  | Gate-Source Leakage Current    | $V_{GS}$ =±20V , $V_{DS}$ =0V |      |      | ±100 | nA   |

#### On Characteristics

| Symbol              | Parameter                          | Conditions                                 | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------------|--------------------------------------------|------|------|------|------|

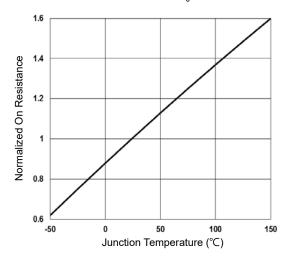

| R <sub>DS(ON)</sub> | IStatic Drain-Source On-Resistance | $V_{GS}$ =10V , $I_D$ =8A                  |      |      | 5.1  | - mΩ |

|                     |                                    | $V_{GS}$ =4.5V , $I_D$ =8A                 |      |      | 11   |      |

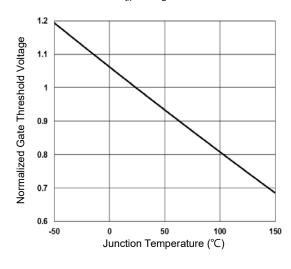

| $V_{GS(th)}$        | Gate Threshold Voltage             | $V_{GS}=V_{DS}$ , $I_D=250uA$              | 1.0  |      | 2.5  | V    |

| gfs                 | Forward Transconductance           | V <sub>DS</sub> =10V , I <sub>DS</sub> =8A |      | 8.6  |      | S    |

#### Dynamic and switching Characteristics (NOTE 4)

| Symbol           | Parameter                    | Conditions                                                                      | Min. | Тур. | Max. | Unit |

|------------------|------------------------------|---------------------------------------------------------------------------------|------|------|------|------|

| $Q_g$            | Total Gate Charge            | 101 101 101 1004                                                                |      | 40.8 |      |      |

| $Q_gs$           | Gate-Source Charge           | V <sub>DS</sub> =10V , V <sub>GS</sub> =10V , I <sub>D</sub> =30A<br>(NOTE 3)   |      | 8.1  |      | nC   |

| $Q_{gd}$         | Gate-Drain Charge            | (14012 9)                                                                       | -    | 7.4  |      |      |

| $T_{d(on)}$      | Turn-On Delay Time           | $V_{DS}$ =10V , $V_{GS}$ =10V , $R_{GEN}$ =2.7 $\Omega$ , $I_{D}$ =30A (NOTE 3) | -    | 7.3  |      |      |

| T <sub>r</sub>   | Rise Time                    |                                                                                 | -    | 75.3 |      | nS   |

| $T_{d(off)}$     | Turn-Off Delay Time          |                                                                                 |      | 36.6 |      | 110  |

| $T_f$            | Fall Time                    |                                                                                 |      | 53   |      |      |

| C <sub>iss</sub> | Input Capacitance            | V <sub>DS</sub> =15V , V <sub>GS</sub> =0V , F=1MHz<br>(NOTE 3)                 | -    | 2117 |      |      |

| C <sub>oss</sub> | Output Capacitance           |                                                                                 | -    | 324  |      | pF   |

| C <sub>rss</sub> | Reverse Transfer Capacitance |                                                                                 |      | 223  |      |      |

| $R_g$            | Gate Resistance              | $V_{GS}$ =0V , $V_{DS}$ =0V , F=1MHz                                            |      | 2.8  |      | Ω    |

#### **Drain-Source Diode Characteristics and Ratings**

| Symbol          | Parameter             | Conditions                 | Min. | Тур. | Max. | Unit |

|-----------------|-----------------------|----------------------------|------|------|------|------|

| V <sub>SD</sub> | Diode Forward Voltage | $V_{GS}$ =0V , $I_{S}$ =1A |      |      | 1    | V    |

#### NOTES:

- 1.  $V_{DD}$ =25V,  $V_{GS}$ =10V, L=0.1mH,  $I_{AS}$ =25A.

- 2. The power dissipation is limited by  $150^{\circ}$ C junction temperature.

- 3. Guaranteed by design, not subject to production.

- 4. The data tested by pulsed , pulse width  $\leq 300 \text{us}$  , duty cycle  $\leq 2\%$ .

#### **Characteristics Curves**

FIG. 1-Continuous Drain Current vs. T<sub>C</sub>

FIG. 2-Normalized RDSON vs. T<sub>J</sub>

FIG. 3-Normalized  $V_{th}$  vs.  $T_{C}$

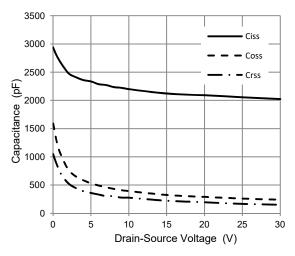

FIG. 4-Capacitance

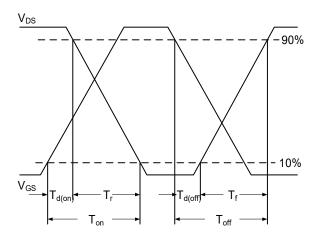

FIG. 5-Switching Time Waveform

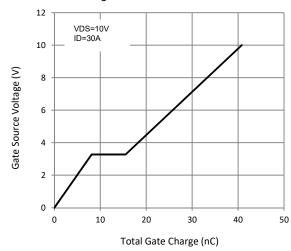

FIG. 6-Gate Charge Characteristics

#### **Characteristics Curves**

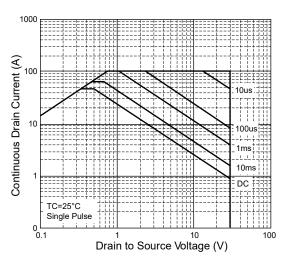

#### FIG. 7-Safe Operating Area

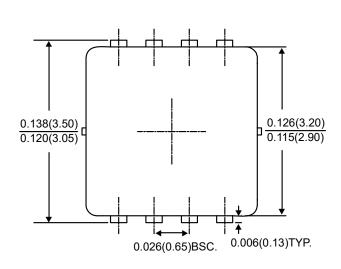

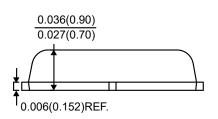

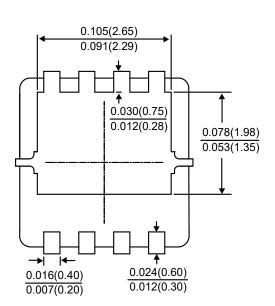

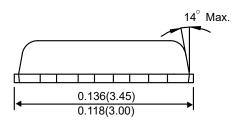

### **Package Outline Dimensions**

#### PPAK3X3

Dimensions in inches and (millimeters)

### LEGAL DISCLAIMER

- The product is provided "AS IS" without any guarantees or warranty. In association with the product, Eris Technology Corporation, its affiliates, and their directors, officers, employees, agents, successors and assigns (collectively, the "Eris") makes no warranties of any kind, either express or implied, including but not limited to warranties of merchantability, fitness for a particular purpose, of title, or of non-infringement of third party rights.

- The information in this document and any product described herein are subject to change without notice and should not be construed as a commitment by Eris. Eris assumes no responsibility for any errors that may appear in this document.

- Eris does not assume any liability arising out of the application or use of this document or any product described herein, any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Eris and all the companies whose products are represented on Eris website, harmless against all damages.

- No license, express or implied, by estoppels or otherwise, to any intellectual property is granted by this document or by any conduct of Eris. Product name and markings notes herein may be trademarks of their respective owners.

- Eris does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- Should Customers purchase or use Eris products for any unintended or unauthorized application, Customers shall indemnify and hold Eris and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

- The official text is written in English and the English version of this document is the only version endorsed by Eris. Any discrepancies or differences created in the translations are not binding and have no legal effect on Eris for compliance or enforcement purposes.