# 4V to 16V Input, Quad-Output Power Module with I<sup>2</sup>C and MTP in Ultra-Thin Package

#### **DESCRIPTION**

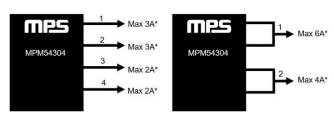

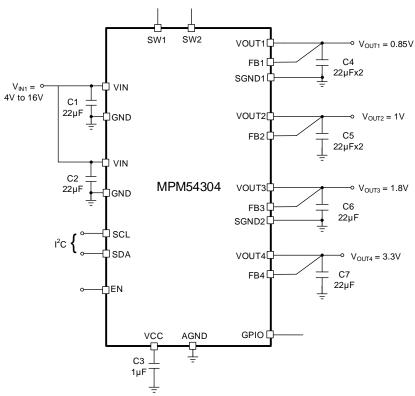

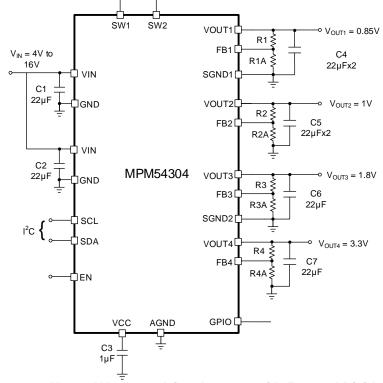

The MPM54304 is a quad-output, DC/DC step-down power module with up to 3A per output (channel 1 and 2) and 2A per output (channel 3 and 4). Channels 1 and 2 can be paralleled to provide up to 6A of current, and channels 3 and 4 can be paralleled to provide up to 4A of current.

Operating over a 4V to 16V input voltage range, the MPM54304 can support an output voltage range of 0.55V to 7V. The output voltage can be set via the I<sup>2</sup>C or external resistor divider. The module has internal auto-compensation, which eliminates the need for an external compensation network. The MPM54304 employs a constant-on-time (COT) control scheme to provide ultra-fast load transient responses. This minimizes the required output capacitance.

The MPM54304 features a two-time, non-volatile programmable memory. Its operating parameters are programmable via the I<sup>2</sup>C.

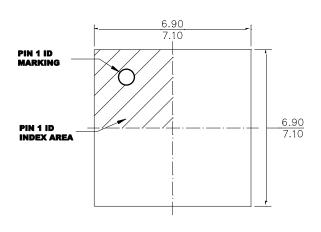

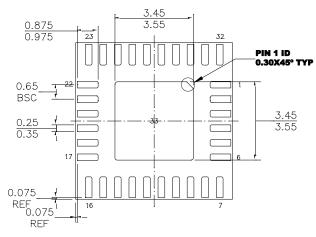

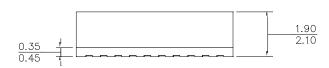

The MPM54304 requires a minimal number of external components, and is available in ultrathin LGA-33 (7mmx7mmx2mm) package.

#### **FEATURES**

- 4V to 16V Operating Input Range

- Wide Output Voltage:

- I<sup>2</sup>C Programmable: 0.55V to 5.4V

- o External Resistor Divider: 0.6V to 7V or  $V_{IN}$  \*  $D_{MAX}$  if  $V_{IN}$  < 7V

- Channel 1 and 2: 3A Continuous Current Channel 3 and 4: 2A Continuous Current

- Interleaved Operation

- Configurable, Multi-Functional GPIO Pin

- I<sup>2</sup>C and Configurable Parameters:

- Paralleling Channel 1 and 2

- Paralleling Channel 3 and 4

- Switching Frequency

- Output Voltage

- Over-Current and Over-Voltage Protection Threshold

- Power-On and Power-Off Sequencing

- Forced PWM or Auto-PWM/PFM

#### **APPLICATIONS**

- FPGA Power Supplies

- Multi-Rail Power Systems

- MCU/DSP Power Supplies

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS", the MPS logo, and "Simple, Easy Solutions" are trademarks of Monolithic Power Systems, Inc. or its subsidiaries.

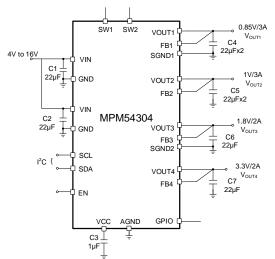

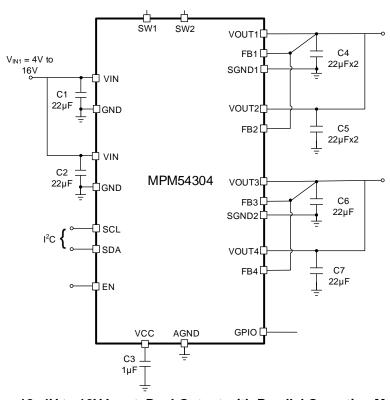

#### TYPICAL APPLICATION

4V to 16V Input and Quad Output

#### Note:

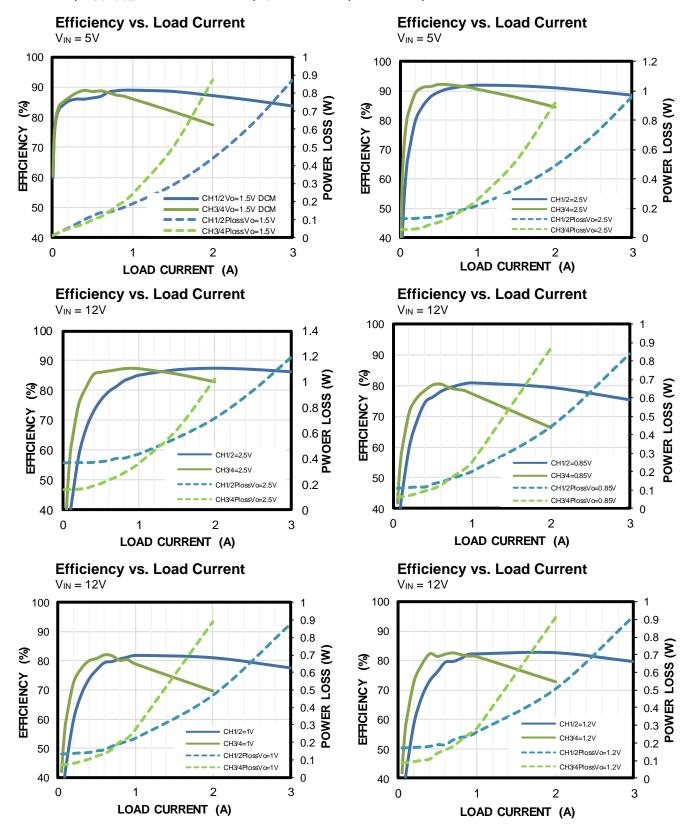

Maximum current per rail is subject to total package power loss derating. See the Max P<sub>LOSS</sub> vs. Temperature Curve on page 11 for the maximum allowed package power loss rating. The total package power loss is determined as the sum of power loss of all rails: P<sub>LOSS</sub> = (P<sub>LOSS</sub>1 + P<sub>LOSS</sub>2 + ... + P<sub>LOSS</sub>n), where n represents the utilized number of rails.

#### ORDERING INFORMATION

| Part Number*     | Part Number* Package |           | Note                                                                         | MSL<br>Rating |

|------------------|----------------------|-----------|------------------------------------------------------------------------------|---------------|

| MPM54304GMN-XXXX | LGA-33<br>(7mmx7mm)  | See Below |                                                                              |               |

| MPM54304GMN-0000 | LGA-33<br>(7mmx7mm)  | See Below | Pre-programmed output voltage or I <sup>2</sup> C adjustable                 |               |

| MPM54304GMN-0001 | LGA-33<br>(7mmx7mm)  | See Below | Set output voltage with resistor divider                                     | 3             |

| MPM54304GMN-0002 | LGA-33<br>(7mmx7mm)  | See Below | Set output voltage with resistor divider; buck 1 & 2 in parallel             | 3             |

| MPM54304GMN-0003 | LGA-33<br>(7mmx7mm)  | See Below | Set output voltage with resistor divider; buck 3 & 4 parallel                |               |

| MPM54304GMN-0004 | LGA-33<br>(7mmx7mm)  | See Below | Set output voltage with resistor divider; buck 1 & 2, buck 3 & 4 in parallel |               |

<sup>\*-</sup>XXXX is the configuration code identifier for register settings stored in the MTP memory. For default configuration with an I<sup>2</sup>C programmed output voltage, the code is "0000". See Tables 3 to 12 on page 42 for the detailed configuration information and the register map of codes "0001" to "0004".

#### **TOP MARKING**

MPSYYWW

MP54304

LLLLLLLL

М

MPS: MPS prefix YY: Year code WW: Week code MP54304: Part number

MP54304: Part number LLLLLLLLL: Lot number

M: Module

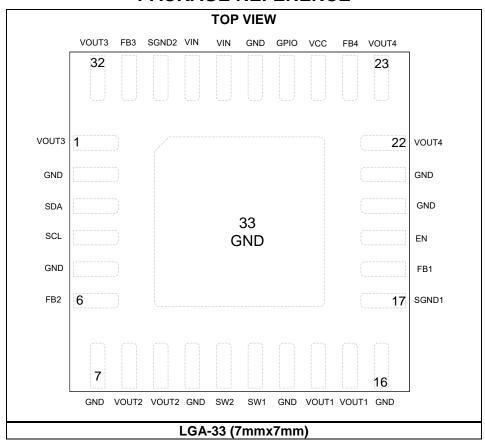

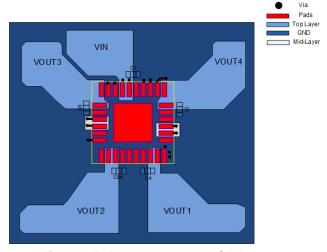

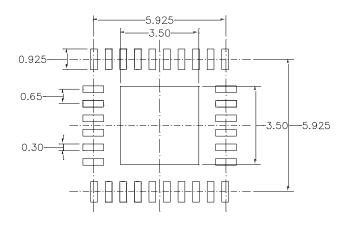

## **PACKAGE REFERENCE**

## **PIN FUNCTIONS**

| Pin #                                  | Name     | Description                                                                                                                                                                                                                                                                    |

|----------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 32                                  | VOUT3    | Channel 3 output.                                                                                                                                                                                                                                                              |

| 2, 5, 7, 10, 13,<br>16, 20, 21, 27, 33 | GND      | Power ground. Connect to GND with wide copper plane and sufficient vias.                                                                                                                                                                                                       |

| 3                                      | SDA      | I <sup>2</sup> C data signal pin.                                                                                                                                                                                                                                              |

| 4                                      | SCL      | I <sup>2</sup> C clock signal pin.                                                                                                                                                                                                                                             |

| 6                                      | FB2      | <b>Feedback of buck 2.</b> Connect buck 2's output directly to this pin or through a feedback resistor divider.                                                                                                                                                                |

| 8, 9                                   | VOUT2    | Channel 2 output.                                                                                                                                                                                                                                                              |

| 11                                     | SW2      | Buck 2 switching node. Connect to SW1 in parallel mode.                                                                                                                                                                                                                        |

| 12                                     | SW1      | Buck 1 switching node. Connect to SW2 in parallel mode.                                                                                                                                                                                                                        |

| 14, 15                                 | VOUT1    | Channel 1 output.                                                                                                                                                                                                                                                              |

| 17                                     | SGND1    | Signal ground 1. Channel 1 and 2 output voltage feedback sense ground.                                                                                                                                                                                                         |

| 18                                     | FB1      | <b>Feedback of buck 1.</b> Connect buck 1's output directly to this pin or through a feedback resistor divider.                                                                                                                                                                |

| 19                                     | EN/SYNCI | <b>Enable control.</b> Apply a logic high voltage on this pin to enable the IC; pull EN/SYNCI to logic low to disable the IC. The EN pin has a $2M\Omega$ internal pull-down resistor. Apply a clock on EN/SYNCI to synchronize the switching frequency to the external clock. |

| 22, 23                                 | VOUT4    | Channel 4 output.                                                                                                                                                                                                                                                              |

| 24                                     | FB4      | <b>Feedback of buck 4.</b> Connect buck 4's output directly to this pin or through a feedback resistor divider.                                                                                                                                                                |

| 25                                     | VCC      | <b>Internal 3.3V LDO output.</b> The driver and control circuits are powered from this voltage. Connect a 1µF decoupling capacitor to this pin.                                                                                                                                |

|                                        |          | <b>General purpose input/output (GPIO) pin – ADD mode.</b> When the MTP/I <sup>2</sup> C configure this pin as "ADD," the pin can program four different I <sup>2</sup> C slave addresses.                                                                                     |

| 26                                     | GPIO     | <b>General purpose input/output (GPIO) pin – PG mode.</b> When the MTP/I <sup>2</sup> C configure this pin as "PG," it is the open-drain power good output. Pull low when any enabled regulator falls below the UV threshold or when all regulators are disabled.              |

|                                        |          | <b>General purpose input/output (GPIO) pin – Output Port mode.</b> When the MTP/I <sup>2</sup> C configure this pin as "Output Port," it outputs high/low logics determined by the related register. Open-drain structure.                                                     |

|                                        |          | <b>General purpose input/output (GPIO) pin – SYNCO mode.</b> When the MTP/I <sup>2</sup> C configure this pin as "SYNCO," it is the sync output. Phase-shift the clock output to sync another device's switching frequency.                                                    |

| 28, 29                                 | VIN      | <b>Supply voltage input.</b> Requires a ceramic capacitor to decouple the input rail.                                                                                                                                                                                          |

| 30                                     | SGND2    | Signal ground 2. Channel 3 and 4 output voltage feedback sense ground.                                                                                                                                                                                                         |

| 31                                     | FB3      | <b>Feedback of buck 3.</b> Connect buck 3's output directly to this pin or through a feedback resistor divider.                                                                                                                                                                |

| <b>ABSOLUTE MAXIMUM F</b>               | RATINGS (2)                 |

|-----------------------------------------|-----------------------------|

| V <sub>IN</sub>                         |                             |

| V <sub>SWx</sub>                        |                             |

| -0.6V (-7V for <10ns) to $V_{INx}$ +    | - 0.3V (22V for             |

| <10ns)                                  |                             |

| EN, FBx                                 | -0.3V to +6V (3)            |

| GPIO, VCC, SCL, SDA                     | 0.3V to +4V                 |

| Continuous power dissipation (T         | $_{A} = 25^{\circ}C)^{(4)}$ |

|                                         |                             |

| Junction temperature                    | 150°C                       |

| Lead temperature                        | 260°C                       |

| Storage temperature                     | 65°C to +150°C              |

| Recommended Operating C                 | Conditions (5)              |

| Input voltage (V <sub>IN</sub> )        | 4V to 16V                   |

| I <sup>2</sup> C-set V <sub>OUT</sub>   |                             |

| External divider set V <sub>OUT</sub>   |                             |

| 0.6V to 7V or V <sub>IN</sub> *         | $D_{MAX}$ if $V_{IN} < 7V$  |

| Operating junction temp $(T_J) \dots$ - | 40°C to +125°C              |

| Thermal Resistance (6) | $oldsymbol{	heta}_{JA}$ | $\boldsymbol{\theta}$ JC |

|------------------------|-------------------------|--------------------------|

| JESD51-7               | 31.8                    | 23 °C/W                  |

| EVM54304-MN-00A        | 31.8                    | .14.4 . °C/W             |

#### Notes:

- 2) Exceeding these ratings may damage the device.

- For the EN/SYNCI pin's rating, see the Enable (EN/SYNCI) description section on page 17.

- 4) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)  $T_A$ ) /  $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 6) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $T_J$  = -40°C to +125°C  $^{(7)}$ , unless otherwise noted.

| Parameter                                       | Symbol                | Condition                                                              | Min   | Тур  | Max   | Units     |

|-------------------------------------------------|-----------------------|------------------------------------------------------------------------|-------|------|-------|-----------|

| Supply current (no switching)                   | I <sub>IN</sub>       | No switching, FB high, PFM                                             |       | 1500 | 2500  | μΑ        |

| Shutdown current                                | I <sub>IN_STD</sub>   | I <sup>2</sup> C and MTP alive                                         |       | 40   | 80    | μA        |

| EN rising threshold                             | V <sub>EN_R</sub>     |                                                                        | -2.5% | 1.21 | +2.5% | V         |

| EN hysteresis                                   | V <sub>EN_</sub> F    |                                                                        |       | 150  |       | mV        |

| EN input current                                | I <sub>EN</sub>       | V <sub>EN</sub> = 2V                                                   |       | 1    |       | μΑ        |

| Frequency SYNC input range <sup>(8)</sup>       | f <sub>SYNCI</sub>    |                                                                        | 500   |      | 1600  | kHz       |

| Default frequency                               | fsw                   | Adjustable by MTP, register value: 0x0d D[7:6] = 01                    | -15%  | 800  | +15%  | kHz       |

| PG UV rising                                    | $V_{PG\_UV\_R}$       |                                                                        | 88%   | 92%  | 97%   | $V_{REF}$ |

| PG UV falling                                   | $V_{PG\_UV\_F}$       |                                                                        |       | 87%  |       | $V_{REF}$ |

| PG rising delay <sup>(9)</sup>                  | t <sub>PG_R_DLY</sub> | MTP adjustable, register value: 0x0e D[4:2] = 000                      |       | 200  |       | μs        |

| PG falling delay (9)                            | t <sub>PG_F_DLY</sub> |                                                                        |       | 50   |       | μs        |

| Power good, output port sink current capability | V <sub>PG_Sink</sub>  | Sink 1mA                                                               |       |      | 0.4   | V         |

| ADD pin voltage threshold 1                     | V <sub>ADD_1</sub>    | To set I <sup>2</sup> C address 1,<br>register value: 0x0e D[7:6] = 00 |       |      | 18%   | Vcc       |

| ADD pin voltage threshold 2                     | V <sub>ADD_2</sub>    | To set I <sup>2</sup> C address 2,<br>register value: 0x0e D[7:6] = 00 | 33%   |      | 45%   | Vcc       |

| ADD pin voltage threshold 3                     | V <sub>ADD_3</sub>    | To set I <sup>2</sup> C address 3,<br>register value: 0x0e D[7:6] = 00 | 56%   |      | 71%   | Vcc       |

| ADD pin voltage threshold 4                     | V <sub>ADD_4</sub>    | To set I <sup>2</sup> C address 4, register value: 0x0e D[7:6] = 00    | 82%   |      |       | Vcc       |

| ADD pin input current                           | I <sub>ADD</sub>      | V <sub>ADD</sub> = 2V                                                  |       | 0    |       | μA        |

| Frequency sync out range                        | f <sub>SYNCO</sub>    | Open-drain                                                             | 500   |      | 1600  | kHz       |

| Frequency sync out duty                         | Dsynco                | Phase shift 180° from buck 1                                           |       | 50   |       | %         |

| VCC UVLO rising                                 | V <sub>CC_R</sub>     |                                                                        | 2.8   | 3    | 3.2   | V         |

| VCC UVLO hysteresis                             | V <sub>CC_HYS</sub>   |                                                                        |       | 100  |       | mV        |

| VCC voltage                                     | Vcc                   | Icc = 0mA                                                              | 3.1   | 3.3  | 3.5   | V         |

| VCC voltage regulation                          | Vcc_rg                | Icc = 0mA to 25mA                                                      |       | 1    |       | %         |

| Thermal shutdown (9) Total                      |                       |                                                                        |       | 160  |       | °C        |

| Thermal hysteresis (9)                          | T <sub>HYS</sub>      |                                                                        |       | 20   |       | °C        |

| Step-Down Regulator                             |                       | •                                                                      | ,     |      | •     |           |

| VIN UVLO rising                                 | V <sub>IN_R</sub>     | Adjustable by MTP,<br>register value: 0x0c D[2:1] = 01                 |       | 4.5  |       | V         |

| VIN UVLO hysteresis                             | V <sub>IN_HYS</sub>   |                                                                        |       | 600  |       | mV        |

## **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 12V,  $T_J$  = -40°C to +125°C  $^{(7)}$ , unless otherwise noted.

| Parameter                        | Symbol                           | Condition                                                              | Min   | Тур  | Max   | Units            |

|----------------------------------|----------------------------------|------------------------------------------------------------------------|-------|------|-------|------------------|

|                                  | V <sub>FB1</sub>                 | Default output of buck 1,<br>register value: 0x02 D[7:0] =<br>00101101 | -1.5% | 1    | +1.5% | V                |

| Feedback voltage accuracy        | V <sub>FB2</sub>                 | Default output of buck 2, register value: 0x05 D[7:0] = 10110111       | -1.5% | 3.3  | +1.5% | ٧                |

| r eedback voltage accuracy       | V <sub>FB3</sub>                 | Default output of buck 3, register value: 0x08 D[7:0] = 01111101       | -1.5% | 1.8  | +1.5% | ٧                |

|                                  | V <sub>FB4</sub>                 | Default output of buck 4, register value: 0x0b D[7:0] = 010111111      | -1.5% | 1.5  | +1.5% | V                |

| Buck 1, Buck 2                   |                                  |                                                                        |       |      |       |                  |

| Low-side current limit           | ILS_Valley1                      | Adjustable by MTP, register value: 0x01 D[4:3] = 10                    | 3.2   | 4.2  | 5.2   | Α                |

| (source)                         | I <sub>LS_Valley2</sub>          | Adjustable by MTP, register value: 0x04 D[4:3] = 01                    | 2     | 3    | 4     | ٨                |

| Low-side current limit (sink)    | I <sub>CL_PWM1</sub>             |                                                                        |       | -2   |       | Α                |

| Minimum on time (9)              | t <sub>ON_MIN1</sub>             |                                                                        |       | 33   |       | ns               |

| Minimum off time (9)             | t <sub>OFF_MIN1</sub>            |                                                                        |       | 113  |       | ns               |

| Output OVP rising threshold      | Vovp1_H                          |                                                                        | 115%  | 120% | 125%  | V <sub>REF</sub> |

| Output OVP recovery threshold    | V <sub>OVP1_L</sub>              |                                                                        |       | 114% |       | V <sub>REF</sub> |

| Output to discharge resistor (9) | R <sub>SW1</sub> /R <sub>S</sub> |                                                                        |       | 45   |       | Ω                |

| Soft-start time of buck 1        | t <sub>SS_B1</sub>               | V <sub>OUT</sub> = 10 to 90%                                           |       | 0.8  |       | ms               |

| Soft-start time of buck 2        | t <sub>SS_B2</sub>               | V <sub>OUT</sub> = 10 to 90%                                           |       | 1.2  |       | ms               |

| Buck 3, Buck 4                   | •                                |                                                                        | •     | •    | •     |                  |

| Low-side current limit           | ILS_Valley3                      | Adjustable by MTP, register value: 0x07 D[4:3] = 00                    | 1.2   | 2    | 3     | ۸                |

| (source)                         | I <sub>LS_Valley4</sub>          | Adjustable by MTP, register value: 0x0a D[4:3] = 01                    | 2     | 3    | 4     | A                |

| Low-side current limit (sink)    | I <sub>CL_PWM2</sub>             | Forced PWM mode, OVP, discharge                                        |       | -1.5 |       | Α                |

| Minimum on time (9)              | ton_min2                         |                                                                        |       | 31   |       | ns               |

| Minimum off time (9)             | t <sub>OFF_MIN2</sub>            |                                                                        |       | 133  |       | ns               |

| Output OVP rising threshold      | V <sub>OVP2</sub> H              |                                                                        | 115%  | 120% | 125%  | V <sub>REF</sub> |

| Output OVP recovery threshold    | V <sub>OVP2_L</sub>              |                                                                        |       | 114% |       | V <sub>REF</sub> |

| Output to discharge resistor (9) | Rsw3/Rs<br>w4                    |                                                                        |       | 45   |       | Ω                |

| Soft-start time of buck 3        | t <sub>SS_B3</sub>               | Vout = 10 to 90%                                                       |       | 0.8  |       | ms               |

| Soft-start time of buck 4        | t <sub>SS_B4</sub>               | Vout = 10 to 90%                                                       |       | 0.7  |       | ms               |

## **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 12V,  $T_J$  = -40°C to +125°C (7), unless otherwise noted.

| Parameter                                          | Symbol              | Condition | Min | Тур | Max | Units |

|----------------------------------------------------|---------------------|-----------|-----|-----|-----|-------|

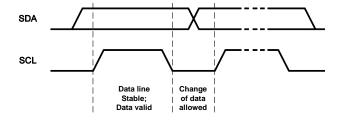

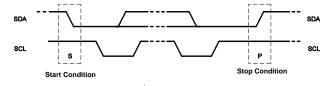

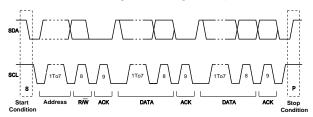

| I <sup>2</sup> C Interface Specifications (        | 10)                 |           |     | •   | •   | •     |

| Input logic high                                   | V <sub>IH</sub>     |           | 1.4 |     |     | V     |

| Input logic low                                    | VIL                 |           |     |     | 0.4 | V     |

| Output voltage logic low                           | V <sub>OUT_L</sub>  | Sink 4mA  |     |     | 0.4 | V     |

| SCL clock frequency                                | fscL                |           |     |     | 3.4 | MHz   |

| SCL high time                                      | tніgн               |           | 60  |     |     | ns    |

| SCL low time                                       | tLOW                |           | 160 |     |     | ns    |

| Data set-up time                                   | tsu.dat             |           | 10  |     |     | ns    |

| Data hold time                                     | thd.dat             |           |     | 70  |     | ns    |

| Set-up time for repeated start                     | t <sub>SU.STA</sub> |           | 160 |     |     | ns    |

| Hold time for repeated start                       | thd.sta             |           | 160 |     |     | ns    |

| Bus free time between a start and a stop condition | t <sub>BUF</sub>    |           | 160 |     |     | ns    |

| Set-up time for stop condition                     | t <sub>SU.STO</sub> |           | 160 |     |     | ns    |

| Rise time of SCL and SDA                           | t <sub>R</sub>      |           | 10  |     | 300 | ns    |

| Fall time of SCL and SDA                           | t⊧                  |           | 10  |     | 300 | ns    |

| Pulse width of suppressed spike                    | tsp                 |           | 0   |     | 50  | ns    |

| Capacitance bus for each bus line                  | Св                  |           |     |     | 400 | pF    |

| SCL low time                                       | $t_{LOW}$           |           | 200 |     |     | ns    |

#### Notes:

- 7) Not tested in production. Guaranteed by over-temperature correlation.

- 8) This function has limitations-only a SYNC IN close to the current system switching frequency can be used.

- 9) Guaranteed by engineering sample characterization.

- 10) Maximum I<sup>2</sup>C bus voltage should be lower than 4V. A 1.8V or 3.3V typical bus voltage is recommended.

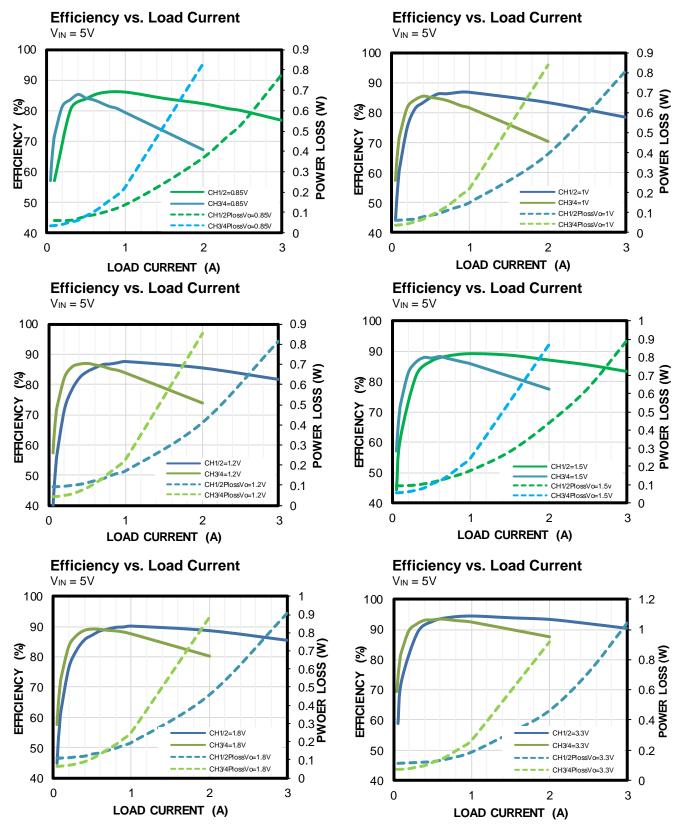

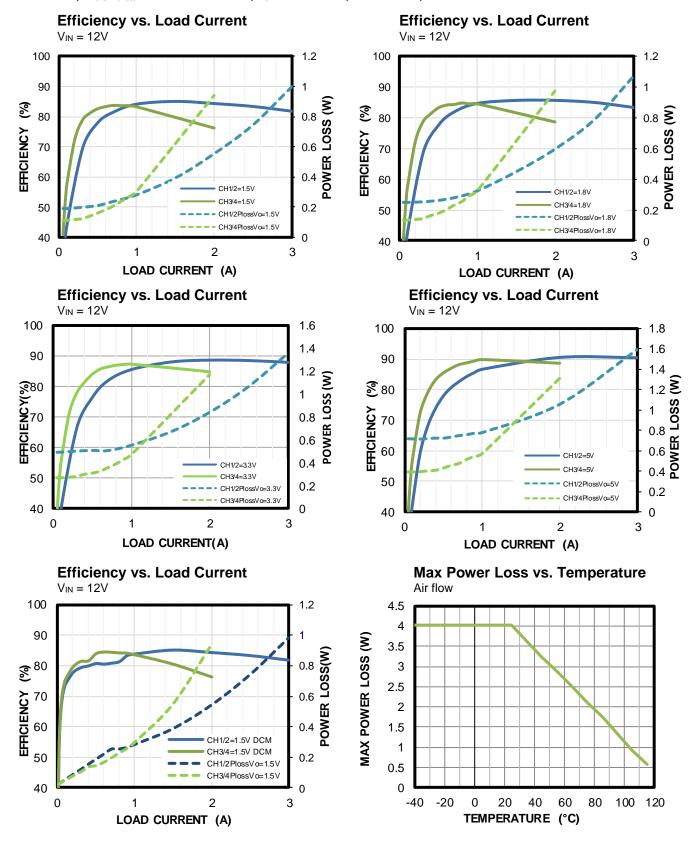

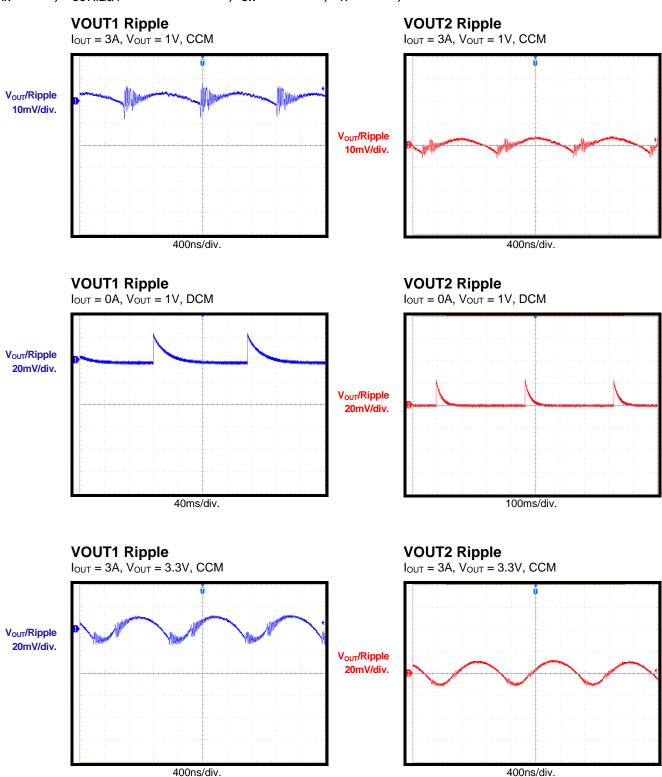

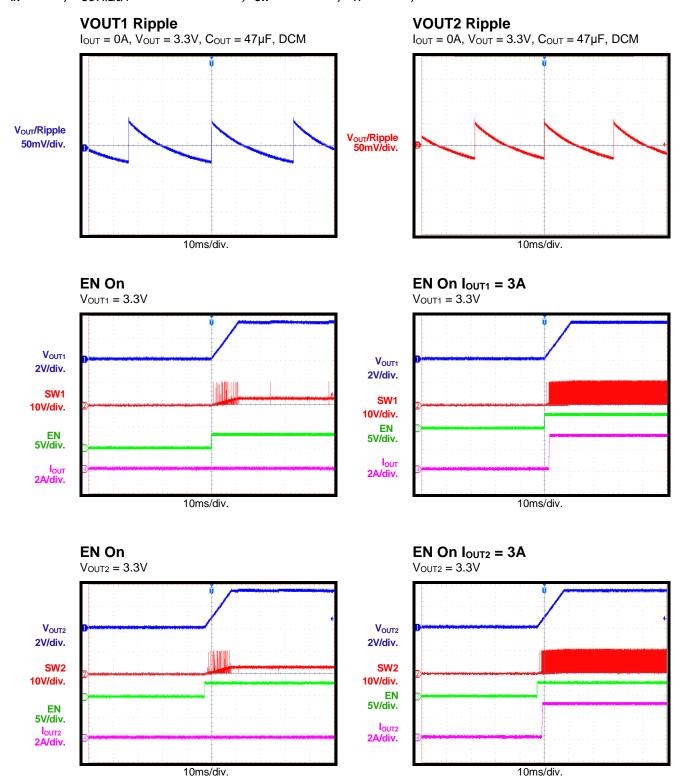

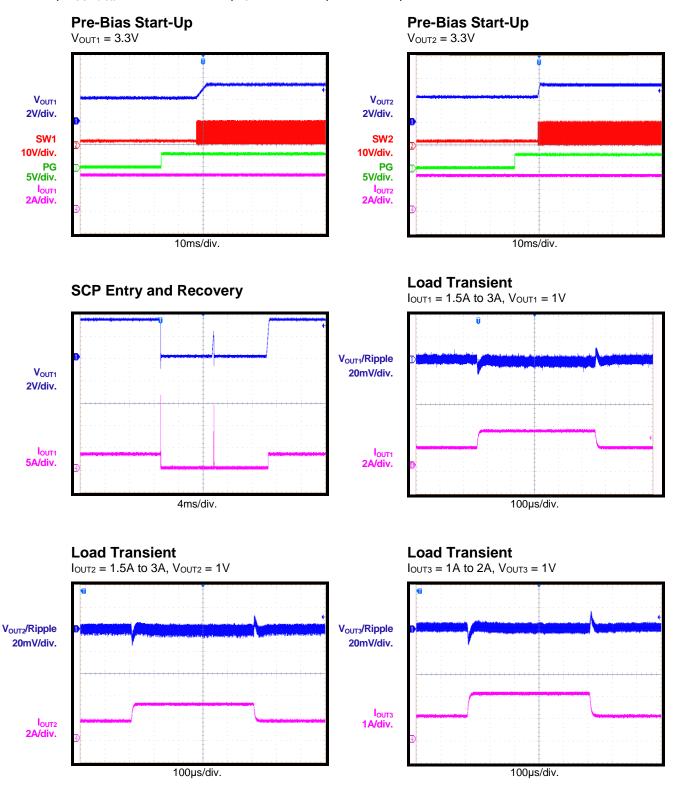

## TYPICAL PERFORMANCE CHARACTERISTICS

100µs/div.

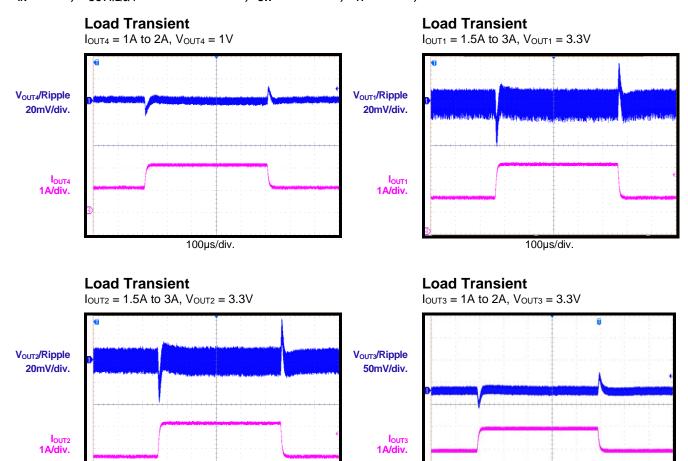

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN} = 12V$ ,  $V_{OUT1/2/3/4} = 1/3.3/1.8/1.5V$ ,  $f_{SW} = 800kHz$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

#### **Load Transient**

$I_{OUT4} = 1A \text{ to } 2A, V_{OU44} = 3.3V$

100µs/div.

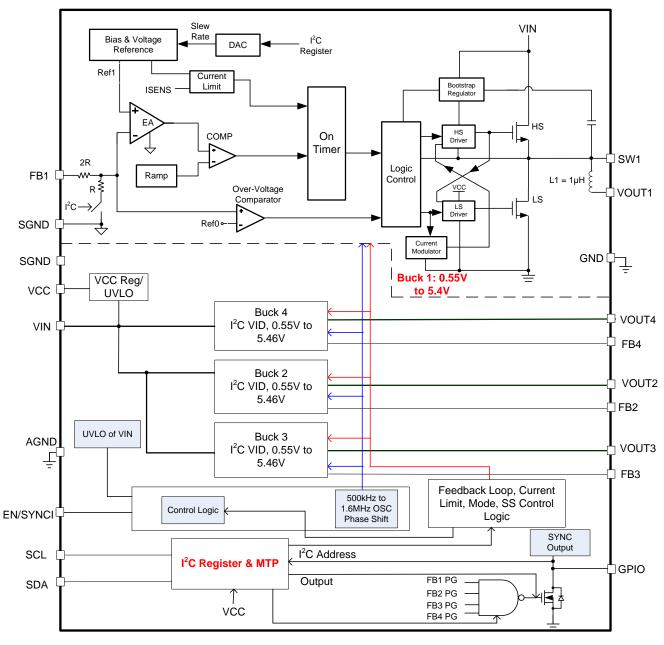

### **FUNCTIONAL BLOCK DIAGRAM**

**Figure 1: Functional Block Diagram**

#### **ANALOG OPERATION**

#### **High-Efficiency Buck Regulators**

The MPM54304 integrates four synchronous, step-down DC/DC regulators that have built-in soft start, compensation, and hiccup current limit protection. Fixed-frequency, constant-on-time (COT) control provides fast transient response. The switching clock is locked and phase-shifted from buck 1 to buck 4 during CCM operation.

#### **Power Supply and UVLO**

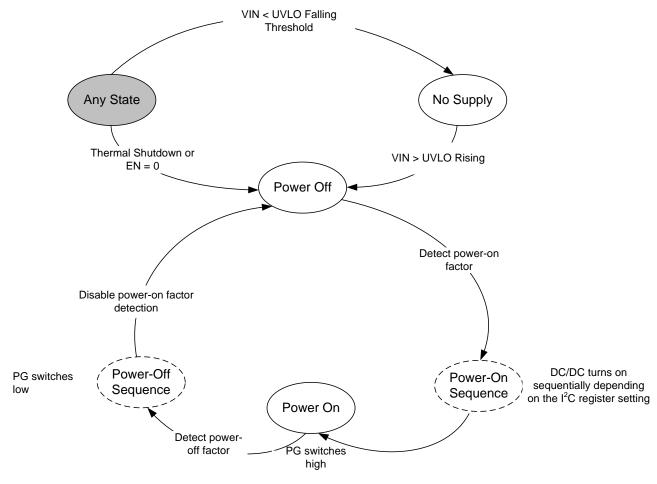

When the input voltage exceeds the UVLO rising threshold voltage, the corresponding buck regulators powers up. It shuts down when the input voltage is below the UVLO falling threshold voltage. See the State Machine Description section on page 32 for more details about power-up.

## Enable and Switching Frequency SYNC Input (EN/SYNCI)

Frequency SYNC input (EN/SYNCI) is a digital control pin that turns the regulator on and off. Drive EN/SYNCI high to turn the regulator on; drive it low to turn the regulator off. When flaoted, EN/SYNCI is pulled low automatically by an internal resistor.

Connecting EN/SYNCI directly to a voltage source requires limiting the amplitude of the voltage source to ≤6V to prevent damage. A resistor divider is required when pulling EN/SYNCI up to a 12V<sub>IN</sub> supply.

For external clock synchronization, connect a clock with a frequency range between 500kHz and 1.6MHz to EN/SYNCI. Buck 1's SW rising edge will synchronize with the external clock rising edge. Select an external clock signal with pulse width less than 1.7µs. After synchronization, the buck 1 to buck 4 phase shift continues to follow the MTP definition. The switching MPM54304's default frequency should be set close to the sync input's frequency. For example, when the external SYNCI clock is 500kHz, the internal switching frequency should be set at 533kHz via the I<sup>2</sup>C or MTP. The I2C and MTP function, including the ADD pin function, is kept active when EN/SYNCI is pulled low.

#### Thermal Shutdown

The MPM54304 features thermal shutdown by internally monitoring the junction temperature of the power module. If the junction temperature exceeds the 160°C threshold, the power modules shuts off. This is a non-latch protection. There is a 20°C hysteresis. Once the junction temperature drops below 140°C, the device initiates a soft start.

#### **Pre-Bias Start-Up**

The MPM54304 has been designed for monotonic start-up into pre-biased loads. If the output is pre-biased to a certain voltage during start-up, the internal BST voltage is refreshed and charged. The voltage on the internal soft-start capacitor is also charged. If the BST voltage exceeds its rising threshold voltage and the soft-start capacitor voltage exceeds the sensed output voltage at the FB pin, the part begins normal operation.

#### Power Good (PG)

The MPM54304 has power good (PG) register bits (bits D4~D7 of the status register), which indicate whether the enabled buck's output voltage is ready or not. When a buck's feedback voltage ( $V_{FB}$ ) is above 92% of the reference voltage ( $V_{REF}$ ), the corresponding PGx bit in the status register is set to from 0 to 1 following a 200 $\mu$ s default or other MTP-programmed delay time. During normal operation, the PGx bit is set to 0 when the corresponding buck regulator falls below the UV threshold with a 50 $\mu$ s delay.

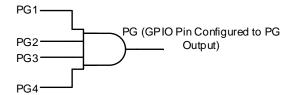

The MPM54304's GPIO pin can be configured as a dedicated PG pin output, as the wire and output of the PG1 to PG4 signals (see Figure 2).

Figure 2: GPIO Pin Configured to PG Output Logic

If UVLO, EN/SYNCI = low, or over-temperature protection (OTP) occurs, the PG pin is pulled

low immediately. If an over-current (OC) condition occurs, the PG pin is pulled low when  $V_{FB}$  drops below 87% of  $V_{REF}$  after a 50 $\mu$ s delay. The PG function does not indicate an output over-voltage condition.

#### **Output Over-Voltage Protection (OVP)**

The MPM54304 monitors the output voltage. If the output voltage exceeds 120% of the regulation voltage for more than 2.5 $\mu$ s, it enters OVP discharge mode. In OVP discharge mode, the low-side MOSFET (LS-FET) turns on and remains on until the low-side current reaches the negative current limit. This discharges the output and tries to keep the output voltage within the normal range. If the OV condition still exists, the LS-FET turns on again after a fixed delay to repeat the discharge behavior. The part exits this discharge mode when V<sub>FB</sub> falls below 114% of V<sub>REF</sub>.

If the input voltage exceeds 18V (the input OVP threshold) during OVP discharge mode, the MPM54304 stops switching until the input voltage falls below 16V. Then the MPM54304 enters discharge mode again. This input OVP function is only active during an output OV condition.

The OVP function can be enabled or disabled through the I<sup>2</sup>C and MTP interface.

#### **Output Discharge**

In order to discharge the energy of the output capacitor during the shutdown sequence, there are discharge resistors (typically  $45\Omega$ ) from the

SWx pin to ground. The discharge function can be enabled or disabled through the I<sup>2</sup>C and MTP interface.

#### Soft Start

The MPM54304 features a soft start (SS) mechanism to ensure smooth output ramp-up during power-up. When the part is enabled and the BST voltage reaches its rising threshold, the internal DAC outputs a ramp voltage (reference voltage). The output voltage smoothly ramps up with the reference voltage. When the DAC output reaches the final voltage, it stops at that level. At this point, soft start finishes and the device enters steady state operation.

The start-up delay and soft-start slew rate are both programmable via the MTP.

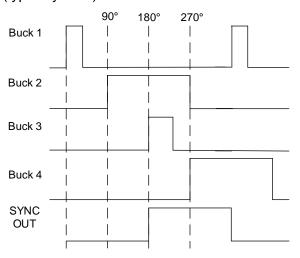

## Out-of-Phase Operation and Clock SYNC Out

Buck 1 to buck 4 are frequency-locked and capable of phase shift. Phase shift is set to a default (described below), but can also be changed by the MTP. When the GPIO pin is configured to "SYNC Out" mode. MPM54304 outputs a 180° phase shift from the internal clock's rising edge with a 50% duty pulse (see Figure 3). This is an open-drain output; an external 1kΩ pull-up resistor should be added. The SYNC Out signal disappears if buck 1 to buck 4 all enter light-load sleep mode. The SYNC Out signal is enabled after the power-on sequence has completed.

Figure 3: Phase Shift Example

#### **VCC** Regulator

A 3.3V internal regulator powers most of the internal circuitries. A decoupling capacitor is needed to stabilize the regulator and reduce the ripple. This regulator takes the  $V_{\text{IN}}$  input and operates in the full  $V_{\text{IN}}$  range.

## Over-Current Protection (OCP) and Short-Circuit Protection (SCP)

The MPM54304 has valley current limit control. The inductor current is monitored during the LS-FET on state. When the sensed inductor current exceeds the valley current limit threshold, the device enters over-current protection (OCP) mode. The HS-FET cannot turn on until the current falls below the valley current limit. Meanwhile, the output voltage drops until it is below the under-voltage (UV) threshold, which is typically 45% below the reference.

If UV and OCP are both triggered, the MPM54304 enters hiccup mode to periodically restart the related power rail. The hiccup duty cycle is very small to reduce power dissipation during a short-circuit condition. During OCP, the device tries to recover from the over-current fault with hiccup mode. To do this, the chip

disables the output power stage, discharges the soft-start capacitor, then automatically tries to soft start again. If the over-current condition still exists when soft start finishes, the device repeats this operation. OCP a is non-latch protection.

#### **Parallel Output Mode**

The outputs of the MPM54304 can be connected in parallel to provide higher current. Output 1 and output 2 can be paralleled to provide up to 6A of current. Output 3 and output 4 can be paralleled to provide up to 4A of current. It should be noted that the maximum output current in parallel mode is also limited by the total power dissipation.

Figure 18 shows the connections for parallel mode operation (see page 41). To operate output 1 and output 2 in parallel mode, connect VOUT1 to VOUT2, and FB1 to FB2. To operate output 3 and output 4 in parallel mode, connect VOUT3 to VOUT4, and FB3 to FB4.

All buck function commands follow buck 1 and buck 3 in parallel mode. The phase delay should be the same for buck 3 and buck 4 when in parallel mode.

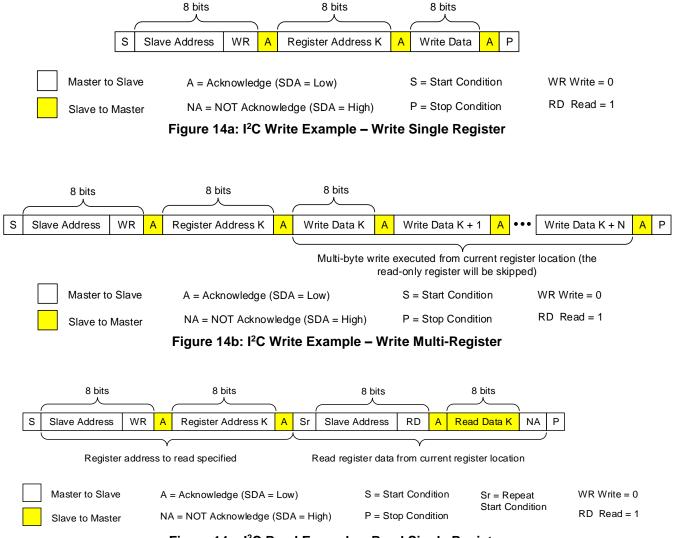

### **DIGITAL INTERFACE**

#### **MTP Program**

The I<sup>2</sup>C and MTP blocks become active once the VCC pin's voltage exceeds its 2V rising

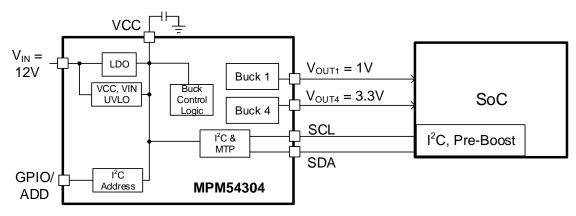

threshold, no matter whether the EN pin's voltage is high or low. Figure 4 shows a system-level application example.

Figure 4: I<sup>2</sup>C Start-Up Block

When VIN powers up and EN/SYNCI is pulled high, the MPM54304 starts up with a "safe mode" that allows the SoC to start up without damage. In safe mode, only one or two power rails will turn on. For example,  $V_{OUT1} = 1V$ ,  $V_{OUT4} = 3.3V$ , other power rails are off. The default buck 1 to buck 4 configuration is determined by the MTP e-fuse.

The MTP data is loaded into the corresponding I<sup>2</sup>C registers during the first power-up. The I<sup>2</sup>C registers directly control the parameters of buck 1 to buck 4. The MTP load to I<sup>2</sup>C register conditions are described below:

• V<sub>CC</sub> > 2V, first power-up.

11/6/2019

MTP programming has been completed.

Toggling EN/SYNCI on and off will not reload the MTP registers into the I<sup>2</sup>C registers again.

The I<sup>2</sup>C register and MTP table are correlated to each other. The MTP table can be accessed and programmed through the I<sup>2</sup>C interface. It can be programmed two times.

After buck 1 and buck 4 power up, the SoC programs the MPM54304 I<sup>2</sup>C register and MTP. For details on how to identify a valid slave address, see the I<sup>2</sup>C Bus Slave Address section on page 30. When the SoC writes to the I<sup>2</sup>C register, the I<sup>2</sup>C register takes effect immediately. It can also be burned into the MTP. The VCC voltage (V<sub>CC</sub>) rises up to 5.2V when the MTP is programmed. In order to protect the device, buck

regulators are shut down when burning the MTP e-fuse. After MTP programming is done, the buck regulators start up sequentially. During normal buck operation, the I<sup>2</sup>C master can read and write the register's data.

### Safety Considerations for Writing MTP

Several protection items can reduce the failure rate of MTP writing. Take the following steps before writing the MTP registers:

Step 1: Set the MTP\_Program bit to 1. The I<sup>2</sup>C register will be locked to prevent write operation until MTP programming finishes; the SoC can read the I<sup>2</sup>C register during this period.

Step 2: Check the MTP burning power supply. If it is above 5.1V, continue the MTP write; otherwise, abort and unlock the I<sup>2</sup>C write protection.

Step 3: The MPM54304 can calculate the sum of all related I<sup>2</sup>C registers to be burned in the MTP register, then generate a 16-bit checksum. This is not a truly sum of all I<sup>2</sup>C registers, but an arithmetic to combine all data. The checksum result is also written to the MTP register.

After the MTP write operation finishes, there is typically a 100ms delay. The MPM54304 then sets the MTP\_Program bit to 0, and the I<sup>2</sup>C register write protection is unlocked. The SoC

can read the I<sup>2</sup>C register; if the MTP\_Program bit goes to 0, it indicates that MTP programming is done.

After the MTP write operation finishes, the SoC can read the MTP register data to confirm that the correct value is saved into the MTP registers. If anything is wrong, the SoC will write the MTP again.

During VIN power-up, before loading the MTP data into the I<sup>2</sup>C register, the MPM54304 does a checksum calculation for all related MTP registers, then compares it with the checksum byte. If they match, the MTP data is loaded into the I<sup>2</sup>C register. Otherwise, the I<sup>2</sup>C register uses the hard-coded default value. There is an I<sup>2</sup>C register flag bit to indicate whether there is a checksum error.

#### **MTP Table**

|        | REG<br>(0x) | D[7]                                       | D[6]                                                                                                                                                                                                  | D[5]                  | D[4]     | D[3]                            | D[2]                   | D[1]             | D[0]             |

|--------|-------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|---------------------------------|------------------------|------------------|------------------|

|        | 40          |                                            |                                                                                                                                                                                                       | Soft Start Delay1     |          |                                 | Soft Start Time1       |                  |                  |

| Buck 1 | 41          | Vout_Limit_<br>EN1                         | Mode1                                                                                                                                                                                                 | Current Lin           | nit1     | VOUT_OVP<br>_EN1                |                        | e Delay<br>lect1 | VOUT_<br>DIS_EN1 |

|        | 42          | Vout_Select1                               |                                                                                                                                                                                                       |                       |          | V_Ref1                          |                        |                  |                  |

|        | 43          |                                            |                                                                                                                                                                                                       | Soft Start De         | elay2    | Additional<br>Phase<br>Delay2   | Soft Start Time2       |                  | ne2              |

| Buck 2 | 44          | Vout_Limit_<br>EN2                         | Mode2                                                                                                                                                                                                 | Current Lin           | nit2     | VOUT_OVP<br>_EN2                |                        | e Delay<br>lect2 | VOUT_<br>DIS_EN2 |

|        | 45          | Vout_Select2                               |                                                                                                                                                                                                       |                       |          | V_Ref2                          |                        |                  |                  |

|        | 46          |                                            |                                                                                                                                                                                                       | Soft Start Delay3     |          |                                 | Soft Start Time3       |                  |                  |

| Buck 3 | 47          | Vout_Limit_<br>EN3                         | Mode3                                                                                                                                                                                                 | Current Lin           | nit3     | VOUT_OVP<br>_EN3                | Phase Delay<br>Select3 |                  | VOUT_<br>DIS_EN3 |

|        | 48          | Vout_Select3                               |                                                                                                                                                                                                       |                       |          | V_Ref3                          |                        |                  |                  |

|        | 49          |                                            |                                                                                                                                                                                                       | Soft Start De         | elay4    | Additional<br>Phase<br>Delay4   | Soft Start Time4       |                  | me4              |

| Buck 4 | 4A          | Vout_Limit_<br>EN4                         | Mode4                                                                                                                                                                                                 | Current Lin           | nit4     | VOUT_OVP<br>_EN4                | Phase Delay<br>Select4 |                  | VOUT_<br>DIS_EN4 |

|        | 4B          | Vout_Select4                               |                                                                                                                                                                                                       |                       | 1        | V_Ref4                          |                        |                  | I                |

| System | 4C          | EN1                                        | EN2                                                                                                                                                                                                   | EN3                   | EN4      |                                 | U\                     | /LO              | OP_BIT           |

| System | 4D          | FREG                                       | Q                                                                                                                                                                                                     | Shutdown_<br>Delay_EN |          | I <sup>2</sup> C                | Slave Add              | ress             |                  |

| System | 4E          | ADD_PG_OP_                                 | SYNCOUT                                                                                                                                                                                               |                       |          | PG_Delay                        |                        | Parallel_<br>2   | Parallel_<br>1   |

| System | 4F          | MTP configure                              | code. "0x00" r                                                                                                                                                                                        | neans standard        | MPM543   | 304; "0x01" mean                | s MPM543               | 304-0001 pa      | art number.      |

| System | 50          | MTP revision nu                            | mber. The cus                                                                                                                                                                                         | •                     | •        | ate the MTP value<br>ored here. | from time              | to time, so      | the revision     |

| System | 51          | registers, ar  • During pow- registers' co | Checksum1 of MTP register 0x40 to 0x50:  When writing the I²C register data into the MTP, the MPM54304 does a checksum of all related I²C registers, and writes the result in this and the next byte. |                       |          |                                 |                        |                  |                  |

| System | 52          |                                            |                                                                                                                                                                                                       | Checksum2 o           | f MTP re | gister 0x40~0x50                | ).                     |                  |                  |

## **MTP Table Description**

| Name                | Bit     | Default                               | Descrip                                                                                                                                                                                                                                                                                                                                                                            | otion                                                       |             |                         |                         |                         |                          |                         |  |

|---------------------|---------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------|-------------------------|-------------------------|-------------------------|--------------------------|-------------------------|--|

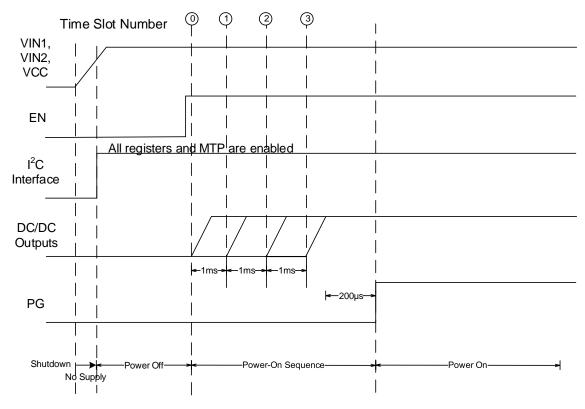

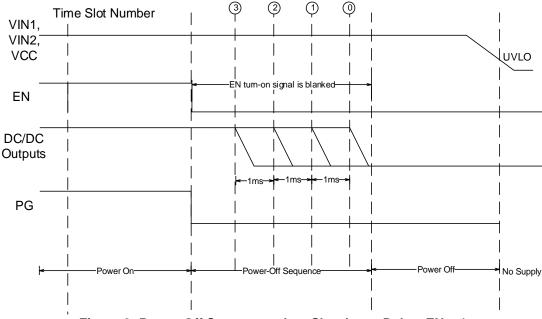

|                     |         | Soft Start<br>Delay1 = 01             |                                                                                                                                                                                                                                                                                                                                                                                    | lay time betw<br>to ramp up. T                              |             |                         |                         |                         | eady to b                | uck Vout                |  |

| Soft-Start          |         | Soft Start<br>Delay2 = 11             | D[5:4] =                                                                                                                                                                                                                                                                                                                                                                           | D[5:4] = 00: 0ms, time slot 0                               |             |                         |                         |                         |                          |                         |  |

| Delay               | D[5:4]  | Soft Start                            | D[5:4] = 01: 1ms, time slot 1<br>D[5:4] = 10: 2ms, time slot 2                                                                                                                                                                                                                                                                                                                     |                                                             |             |                         |                         |                         |                          |                         |  |

|                     |         | Delay3 = 01                           | D[5:4] =                                                                                                                                                                                                                                                                                                                                                                           | : 11: 3ms, time                                             | e slot 3    |                         |                         |                         |                          |                         |  |

|                     |         | Soft Start<br>Delay4 = 10             | See the                                                                                                                                                                                                                                                                                                                                                                            | Power-On Se                                                 | equence se  | ection on pa            | age 33 for tl           | he time slo             | t definition             | ١.                      |  |

|                     |         | Delay1 = 0                            |                                                                                                                                                                                                                                                                                                                                                                                    |                                                             |             |                         |                         |                         |                          |                         |  |

| Additional<br>Phase | D[3]    | Delay2 = 0                            | Set to 1                                                                                                                                                                                                                                                                                                                                                                           | to add a 100i                                               | ne nhaea n  | lelay for the           | huck high-              | eida ewitc              | h turn-on 4              | adae                    |  |

| Delay               | D[3]    | Delay3 = 0                            | 361101                                                                                                                                                                                                                                                                                                                                                                             | to add a 100i                                               | is priase c | lelay for the           | buck High               | SIGE SWILL              | ii tuiii-oii e           | euge.                   |  |

|                     |         | Delay4 = 0                            |                                                                                                                                                                                                                                                                                                                                                                                    |                                                             |             |                         |                         |                         |                          |                         |  |

|                     |         |                                       | internal                                                                                                                                                                                                                                                                                                                                                                           | rt slew rate s<br>reference vol<br>times the val            | tage slew   |                         |                         |                         |                          |                         |  |

|                     | _       | Soft Start<br>Time1 = 010             | D[3:0] = 000: 2.67mV/ $\mu$ s soft-start slew rate<br>D[3:0] = 001: 1.6mV/ $\mu$ s soft-start slew rate<br>D[3:0] = 010: 1mV/ $\mu$ s soft-start slew rate<br>D[3:0] = 011: 0.67mV/ $\mu$ s soft-start slew rate<br>D[3:0] = 101: 0.25mV/ $\mu$ s soft-start slew rate<br>D[3:0] = 110: 0.167mV/ $\mu$ s soft-start slew rate<br>D[3:0] = 111: 0.1mV/ $\mu$ s soft-start slew rate |                                                             |             |                         |                         |                         |                          |                         |  |

|                     |         | Soft Start<br>Time2 = 011             |                                                                                                                                                                                                                                                                                                                                                                                    | Available soft-start time vs. the V <sub>OUT</sub> voltage: |             |                         |                         |                         |                          |                         |  |

| Soft-Start<br>Time  | D[2:0]  | Soft Start                            | Soft-st                                                                                                                                                                                                                                                                                                                                                                            | art time (ms):                                              | Vout =      | V                       | V                       | V                       | V                        | V                       |  |

|                     |         | Time3 = 001                           | Bits                                                                                                                                                                                                                                                                                                                                                                               | (mV/µs)                                                     | 5V          | V <sub>OUT</sub> = 3.3V | V <sub>OUT</sub> = 2.5V | V <sub>оит</sub> = 1.8V | V <sub>оит</sub> =<br>1V | V <sub>OUT</sub> = 0.6V |  |

|                     |         | Soft Start<br>Time4 = 001             | 000                                                                                                                                                                                                                                                                                                                                                                                | 2.67                                                        | 0.6         | 0.4                     | 0.3                     | 0.7                     | 0.4                      | 0.2                     |  |

|                     |         |                                       | 001                                                                                                                                                                                                                                                                                                                                                                                | 1.6                                                         | 1.0         | 0.7                     | 0.5                     | 1.1                     | 0.6                      | 0.4                     |  |

|                     |         |                                       | 010                                                                                                                                                                                                                                                                                                                                                                                | 1                                                           | 1.7         | 1.1                     | 0.8                     | 1.8                     | 1.0                      | 0.6                     |  |

|                     |         |                                       | 011                                                                                                                                                                                                                                                                                                                                                                                | 0.67                                                        | 2.5         | 1.6                     | 1.2                     | 2.7                     | 1.5                      | 0.9                     |  |

|                     |         |                                       | 100                                                                                                                                                                                                                                                                                                                                                                                | 0.4                                                         | 4.2         | 2.8                     | 2.1                     | 4.5                     | 2.5                      | 1.5                     |  |

|                     |         |                                       | 101                                                                                                                                                                                                                                                                                                                                                                                | 0.25                                                        | 6.7         | 4.4                     | 3.3                     | 7.2                     | 4.0                      | 2.4                     |  |

|                     |         |                                       | 110                                                                                                                                                                                                                                                                                                                                                                                | 0.167                                                       | 10.0        | 6.6                     | 5.0                     | 10.8                    | 6.0                      | 3.6                     |  |

|                     |         |                                       | 111                                                                                                                                                                                                                                                                                                                                                                                | 0.1                                                         | 16.7        | 11.0                    | 8.3                     | 18.0                    | 10.0                     | 6.0                     |  |

|                     | EN1 = 1 | Vout_Limit_<br>EN1 = 1<br>Vout_Limit_ | Thic hit                                                                                                                                                                                                                                                                                                                                                                           | limits the max                                              | rimum outr  | out voltage             | of each now             | vor rail                |                          |                         |  |

| Vout_Limit          | D:-:    | EN2 = 0                               |                                                                                                                                                                                                                                                                                                                                                                                    | : The maximu                                                | •           | •                       | •                       |                         | the 120 \/-              | NIT                     |  |

| _EN                 | D[7]    | Vout_Limit_<br>EN3 = 0                | setting,                                                                                                                                                                                                                                                                                                                                                                           | maximum duty<br>: The maximu                                | cycle, or a | bsolute volt            | age limit.              | •                       |                          |                         |  |

|                     |         | Vout_Limit_<br>EN4 = 0                |                                                                                                                                                                                                                                                                                                                                                                                    |                                                             |             |                         |                         |                         |                          |                         |  |

| Mode                     | D[6]   | Mode1 = 1<br>Mode2 = 1<br>Mode3 = 1<br>Mode4 = 1                                                                         | Selects the mode (auto-PFM/PWM mode or forced PWM mode).  D[6] = 0: Auto-PFM/PWM mode  D[6] = 1: Forced PWM mode                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------|--------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Current<br>Limit         | D[5:4] | Current Limit1 = 10  Current Limit2 = 10  Current Limit3 = 01  Current Limit4 = 01                                       | Sets the current limit of buck 1 to buck 4.  D[5:4] = 00: 2A valley current limit for 1A output current application D[5:4] = 01: 3A valley current limit for 2A output current application D[5:4] = 10: 4.2A valley current limit for 3A output current application D[5:4] = 11: 5A valley current limit for 4A peak output current application  Note: For buck 3 and buck 4, a 4.2A or 5A valley current limit is not available; D[5:4] = 10 or 11 are both invalid. |

| Phase<br>Delay<br>Select | D[2:1] | Phase Delay<br>Select1 = 01<br>Phase Delay<br>Select2 = 10<br>Phase Delay<br>Select3 = 11<br>Phase Delay<br>Select4 = 00 | Sets the phase delay.  00: 0° delay  01: 90° delay  10: 180° delay  11: 270° delay                                                                                                                                                                                                                                                                                                                                                                                    |

| VOUT_<br>OVP_EN          | D[3]   | VOUT_OVP_<br>EN1 = 1<br>VOUT_OVP_<br>EN2 = 1<br>VOUT_OVP_<br>EN3 = 1<br>VOUT_OVP_<br>EN4 = 1                             | Enable bit of buck 1 to buck 4's output over-voltage protection (OVP) function.  D[3] = 0: Disable OVP function  D[3] = 1: Enable OVP function                                                                                                                                                                                                                                                                                                                        |

| VOUT_<br>DIS_EN          | D[0]   | VOUT_DIS_<br>EN1 = 1<br>VOUT_DIS_<br>EN2 = 1<br>VOUT_DIS_<br>EN3 = 1<br>VOUT_DIS_<br>EN4 = 1                             | Enable bit of buck 1 to buck 4's output discharge function.  D[3] = 0: Disable discharge function  D[3] = 1: Enable discharge function                                                                                                                                                                                                                                                                                                                                |

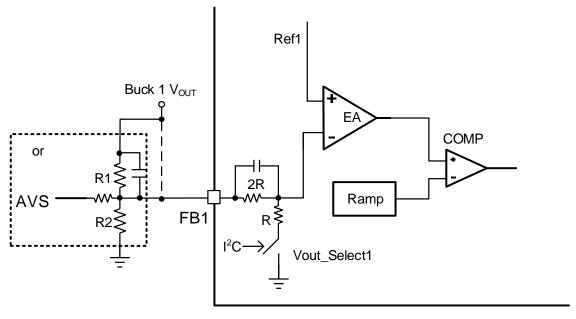

| Vout_<br>Select          | D[7]   | Vout_Select1 = 0  Vout_Select2 = 1  Vout_Select3 = 1  Vout_Select4 = 1                                                   | Selects the internal feedback divider ratio.  D[7] = 0: The FB voltage is fed directly to the error amplifier. The FB voltage is equal to the reference voltage  D[7] = 1: The FB voltage is divided by 1/3, then compared with the reference voltage. The FB voltage is equal to 2 times the reference voltage  Note: If the AVS function is used, the D[7] bit will be set at 0.                                                                                    |

|                                   |        | V 5 .:                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------|--------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V_Ref                             | D[6:0] | V_Ref1 = 1.V<br>V_Ref2 = 3.3V<br>V_Ref3 = 1.800V<br>V_Ref4 = 2.5V | Sets the internal reference voltage, from 550mV to 1.82V, 10mV per step. The voltage slew rate is fixed at 2mV/ $\mu$ s.<br>D[6:0] = 000 0000: 550mV   D[6:0] = 000 0001: 560mV     D[6:0] = 111 1111: 1.82V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| EN1, EN2,<br>EN3, EN4             | D[7:4] | EN1 = 1<br>EN2 = 1<br>EN3 = 1<br>EN4 = 1                          | Enable bit of each buck regulator.  1: Enabled 0: Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| UVLO                              | D[2:1] | D[2:1] = 01                                                       | Sets the input UVLO threshold of VIN.  00: UVLO rising threshold is 3.5V  01: UVLO rising threshold is 4.5V  10: UVLO rising threshold is 5.8V  11: UVLO rising threshold is 8.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

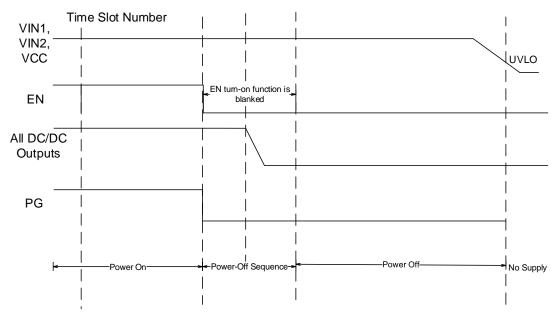

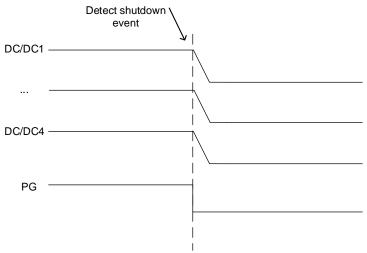

| OP_BIT                            | D[0]   | D[0] = 0                                                          | When the ADD_PG_OP_SYNCOUT bit is set to 10, pin 20 is configured as a GPIO output port. OP_BIT sets the output port as logic high or low. This bit is only valid when ADD_PG_OP_SYNCOUT = 10.  0: Pin 20 pulls low, with certain resistance 1: Pin 20 is an open drain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |