# USB Audio Controller with Headphone Driver & with Microphone/Line-in Interface

#### **Features**

- Compliant with USB Specification v1.1, and USB 2.0 full speed

- Compliant with USB 3.0 super speed operation

- Embedded stereo ADC with Microphone Boost

- Embedded Power-On-Reset circuit

- Embedded Headphone driver

- Support I2S input (master and slave mode) and I2S output interface (master mode)

- Support sampling frequency 44.1/48kHz for playback and recording

- Pin to set recording source from internal ADC or external ADC

- Pin to set Headphone mode or I2S output mode

- Support Microphone and line-in function switching

- Support volume/mute control with external button

- LED indicator function for playback, mute and recording mute

- Support 3D surround sound

- Support Microphone bias

- Support Digital microphone interface for recording

- Power Clipping function for speaker protection

- External EEPROM interface for vendor specific and hardware configuration via I2C

- I2S input port allows AD62556 to receive ESMT's high performance ADC(i.e. AD12250)

- I2S output port allows AD62556 to control ESMT's high performance audio devices (i.e. AD82586/AD82581)

- Built-in 5V to 3.3V regulator for internal device operation

- Anti-pop design

- Over-temperature protection

- Under-voltage shutdown

- Short-circuit detection

- Single 12 MHz Crystal Input

- 3.3V operation I/O

- Supports Windows Me/2000/XP/Vista/7/8, Linux and MacOS

- Integration circuit quality meet Win7 and Win8 Hardware Logo requirement

#### **Description**

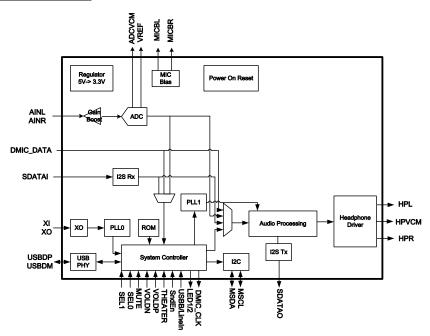

AD62556 is a highly integrated USB single chip for headphone. Many useful features are programmable with pins or I2C control. The device also has an I<sup>2</sup>S input port and I<sup>2</sup>S output port. The I<sup>2</sup>S input port allows other external audio sources to use the class D amplifier to share the headphone. The I<sup>2</sup>S output port allows other high performance audio device (i.e. AD82586/AD82581B).

#### **Functional Block Diagram**

Elite Semiconductor Microelectronics Technology Inc.

Publication Date: Aug. 2021

Revision: 1.1 1/34

#### **Order Informaton**

| Product ID      | Package                | Packing / MPQ                                                        | Comments |

|-----------------|------------------------|----------------------------------------------------------------------|----------|

| AD62556-LG48NAY | E-LQFP-48L<br>(7x7 mm) | 2.5K Units / Small Box<br>(250 Units / Tray, 10 Trays /<br>Small Box | Green    |

## **Available Package**

| Package Type | Device No. | θ <sub>ja</sub> (°C/W) | Ψ <sub>jt</sub> (°C/W) | θ <sub>jt</sub> (°C/W) | Exposed Thermal Pad |

|--------------|------------|------------------------|------------------------|------------------------|---------------------|

| E-LQFP-48L   | AD62556    | 27.4                   | 1.33                   | 6.0                    | Yes (Note1)         |

- Note 1.1: The thermal pad is located at the bottom of the package. To optimize thermal performance, soldering the thermal pad to the PCB's ground plane is suggested.

- Note 1.2:  $\theta_{ja}$  is simulated on a room temperature ( $T_A$ =25 $^{\circ}$ C), natural convection environment test board, which is constructed with a thermally efficient, 4-layers PCB (2S2P). The simulation is tested using the JEDEC51-5 thermal measurement standard.

- Note 1.3:  $\Psi_{jt}$  represents the heat resistance for the heat flow between the chip and the package's top surface. It is extracted from the simulation data to obtain  $\theta_{ja}$ .

- Note 1.3:  $\theta_{jt}$  represents the heat resistance for the heat flow between the chip and the package's top surface. It is simulated a cold plate on the top of the package.

#### **Marking Information**

AD62556

Line 1: LOGO

Line 2: Product no.

Line 3: Tracking Code

Line 4 : Date Code

Publication Date: Aug. 2021

Revision: 1.1 2/34

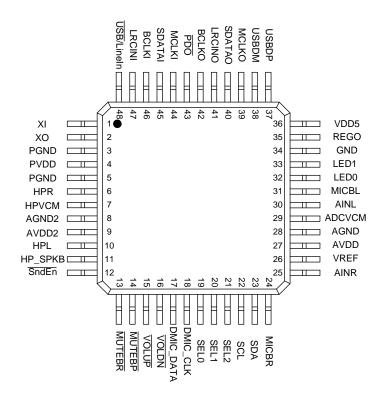

## **Pin Assignment**

# **Pin Description**

| Pin | Name    | Туре | Description                                  | Characteristics                                         |

|-----|---------|------|----------------------------------------------|---------------------------------------------------------|

| 1   | XI      | I    | Crystal input                                | With internal 1Mohm resistor connected to the pin of XO |

| 2   | ХО      | 0    | Crystal output                               |                                                         |

| 3   | PGND    | Р    | Ground                                       |                                                         |

| 4   | PVDD    | Р    | Supply 5V                                    |                                                         |

| 5   | PGND    | Р    | Ground                                       |                                                         |

| 6   | HPR     | 0    | Headphone right channel output               |                                                         |

| 7   | HPVCM   | 0    | Headphone common-mode voltage decoupling pin |                                                         |

| 8   | AGND2   | Р    | Headphone ground                             |                                                         |

| 9   | AVDD2   | Р    | Headphone 5V supply                          |                                                         |

| 10  | HPL     | 0    | Headphone left channel output                |                                                         |

| 11  | HP_SPKB | I    | 0:I2S output mode 1:headphoone mode          | 3.3V Schmitt trigger TTL input buffer                   |

| 12  | SndEn   | I    | Surround enable                              | With internal 100kohm pull-up resistor                  |

| 13  | MUTEBR  | I    | Recording Mute                               | With internal 100kohm pull-up resistor                  |

Elite Semiconductor Microelectronics Technology Inc.

Publication Date: Aug. 2021 Revision: 1.1 3/34

| 14 | MUTEBP    | I   | Power-down and mute of headphone                           | With internal 100kohm pull-up resistor |

|----|-----------|-----|------------------------------------------------------------|----------------------------------------|

| 15 | VOLUP     | I   | Volume up, low active                                      | With internal 100kohm pull-up resistor |

| 16 | VOLDN     | I   | Volume down, low active                                    | With internal 100kohm pull-up resistor |

| 17 | DMIC_DATA | I   | Data input from digital microphone module                  | 3.3V Schmitt trigger TTL input buffer  |

| 18 | DMIC_CLK  | 0   | Clock output to digital microphone module                  |                                        |

|    |           |     | SEL0 = 0: with external amplifier, AD82581                 |                                        |

| 19 | SEL0      | I   | SEL0 = 1: with external amplifier,                         |                                        |

|    |           |     | AD82586/AD83586                                            |                                        |

| 20 | SEL1      | ,   | SEL1 = 0: internal ADC input                               |                                        |

| 20 | SELI      | ı   | SEL1 = 1: external ADC input                               |                                        |

|    |           |     | SEL1 = 0;                                                  |                                        |

|    |           |     | SEL2 = 1 : ADC as Microphone;                              |                                        |

| 21 | SEL2      | ı   | SEL2 = 0: ADC as Line-in                                   |                                        |

| 21 | SELZ      | ı   | SEL1 = 1;                                                  |                                        |

|    |           |     | SEL2 = 1 : Digital microphone input ;                      |                                        |

|    |           |     | SEL2 = 0 : External ADC input                              |                                        |

| 22 | SCL       | I/O | l <sup>2</sup> C's SCL, with a 4.7kohm pull high (this pin |                                        |

| 22 | SCL       | 1/0 | floating is prohibited)                                    |                                        |

| 23 | SDA       | I/O | I <sup>2</sup> C's SDA, with a 4.7kohm pull high (this pin |                                        |

| 23 | SDA       | 1/0 | floating is prohibited)                                    |                                        |

| 24 | MICBR     | 0   | Microphone right channel voltage supply                    |                                        |

| 24 | WIGHT     | 0   | (3mA)                                                      |                                        |

| 25 | AINR      | I   | Analog signal right channel                                |                                        |

| 26 | VREF      | 0   | Reference voltage                                          |                                        |

| 27 | AVDD      | Р   | ADC's 3.3V supply                                          |                                        |

| 28 | AGND      | Р   | ADC's Ground                                               |                                        |

| 29 | ADCVCM    | 0   | ADC common mode voltage decoupling pin                     |                                        |

| 30 | AINL      | I   | Analog signal left channel                                 |                                        |

| 31 | MICBL     | 0   | Microphone Left channel voltage supply                     |                                        |

| 31 | WIICEL    |     | (3mA)                                                      |                                        |

| 32 | LED0      | 0   | LED indicator for playback                                 |                                        |

| 33 | LED1      | 0   | LED indicator for recording                                |                                        |

| 34 | GND       | Р   | Ground                                                     |                                        |

| 35 | REGO      | Р   | 3.3V regulator output                                      |                                        |

| 36 | VDD5      | Р   | 5V supply voltage                                          |                                        |

| 37 | USBDP     | I/O | USB data D+                                                | With internal 1.5kohm pull-up resistor |

|    |           |     |                                                            |                                        |

Publication Date: Aug. 2021 Revision: 1.1 4/34

|    | T          |     | l                                                                                                                                                                                                                                                                  |                                       |

|----|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 38 | USBDM      | I/O | USB data D-                                                                                                                                                                                                                                                        |                                       |

| 39 | MCLKO      | 0   | AD8XXX series Master clock(256xFs)                                                                                                                                                                                                                                 |                                       |

| 40 | SDATAO     | 0   | AD8XXX series Serial audio output                                                                                                                                                                                                                                  |                                       |

| 41 | LRCINO     | 0   | AD8XXX series L/R clock output                                                                                                                                                                                                                                     |                                       |

| 42 | BCLKO      | 0   | AD8XXX series BCLK output                                                                                                                                                                                                                                          |                                       |

| 43 | PDO        | 0   | Power-down output indicator pin  USB/LineIn = 0;  PDO = Low during USB device  unconfiguration  PDO = High during USB device configuration  USB/LineIn = 1;  PDO = Low during D+/D- at reset state  (USBDP=0, USBDM=0)  PDO = High during D+/D- at non-reset state |                                       |

| 44 | MCLKI      | I/O | ADC I2S Master clock (256xFs) input port                                                                                                                                                                                                                           |                                       |

| 45 | SDATAI     | I   | Serial audio data input                                                                                                                                                                                                                                            | 3.3V Schmitt trigger TTL input buffer |

| 46 | BCLKI      | I/O | ADC I2S BCLK input port                                                                                                                                                                                                                                            |                                       |

| 47 | LRCINI     | I/O | ADC I2S L/R clock input port                                                                                                                                                                                                                                       |                                       |

| 48 | USB/LineIn | I   | Output source select pin;  USB/LineIn = 0: USB mode  USB/LineIn = 1: Line-in mode                                                                                                                                                                                  | 3.3V Schmitt trigger TTL input buffer |

Publication Date: Aug. 2021 Revision: 1.1 5/34

# **Absolute Maximum Ratings**

| Symbol           | Parameter                              | Min  | Max | Units |

|------------------|----------------------------------------|------|-----|-------|

| VDD5             | Supply for regulator input pin of VDD5 | -0.3 | 6   | V     |

| PVDD             | Supply for the pin of PVDD             | -0.3 | 6   | V     |

| AVDD2            | Supply for the pin of AVDD2            | -0.3 | 6   | V     |

| AVDD             | Supply for the pin of AVDD             | -0.3 | 3.6 | V     |

| Vi               | Input Pin Voltage                      | -0.3 | 3.6 | V     |

| T <sub>stg</sub> | Storage Temperature                    | -65  | 150 | °C    |

| TJ               | Junction Operating Temperature         | 0    | 150 | °C    |

# **Recommended Operating Conditions**

| Symbol         | Parameter                              | Тур       | Units |

|----------------|----------------------------------------|-----------|-------|

| VDD5           | Supply for regulator input pin of VDD5 | 4.5~5.5   | V     |

| PVDD           | Supply for the pin of PVDD             | 4.5~5.5   | V     |

| AVDD2          | Supply for the pin of AVDD2            | 4.5~5.5   | V     |

| AVDD           | Supply for the pin of AVDD             | 3.15~3.45 | V     |

| TJ             | Junction Operating Temperature         | 0~125     | °C    |

| T <sub>A</sub> | Ambient Operating Temperature          | 0~70      | °C    |

# **Digital Characteristics**

| Symbol          | Parameter                 | Min | Тур | Max        | Units |

|-----------------|---------------------------|-----|-----|------------|-------|

| V <sub>IH</sub> | High-Level Input Voltage  | 2.0 |     | 3.45       | V     |

| V <sub>IL</sub> | Low-Level Input Voltage   |     |     | 0.8        | V     |

| V <sub>OH</sub> | High-Level Output Voltage | 2.4 |     | $V_{REGO}$ | V     |

| V <sub>OL</sub> | Low-Level Output Voltage  |     |     | 0.4        | V     |

| Cı              | Input Capacitance         |     | 6.4 |            | pF    |

Publication Date: Aug. 2021 Revision: 1.1 6/34

# **General Electrical Characteristics**

$\bullet$  Condition:  $T_A \!\!=\!\! 25^{\circ}\! \mathbb{C}$  unless otherwise specified.

| Symbol              | Parameter                                  | Condition | Min  | Тур | Max  | Units |

|---------------------|--------------------------------------------|-----------|------|-----|------|-------|

| I <sub>PD</sub>     | Supply current during suspend mode         |           |      | 350 |      | uA    |

|                     | USB controller operation current           | 3.3V      |      | 75  |      | mA    |

| $V_{REGO}$          | Regulator output voltage                   | 4.5V≦VDD5 | 3.15 | 3.3 | 3.45 | V     |

| V REGO              | Regulator current limit                    | ≦5.5V     |      |     | 100  | mA    |

| т                   | Junction temperature for driver shutdown   |           |      | 150 |      | °C    |

| T <sub>SENSOR</sub> | Temperature hysteresis for recovery        |           |      | 30  |      | °C    |

| UV <sub>H</sub>     | Under voltage disabled (for VDD5 and PVDD) |           |      | 3.8 |      | V     |

| UV <sub>L</sub>     | Under voltage enabled (for VDD5 and PVDD)  |           |      | 3.7 |      | V     |

Publication Date: Aug. 2021 Revision: 1.1 **7/34**

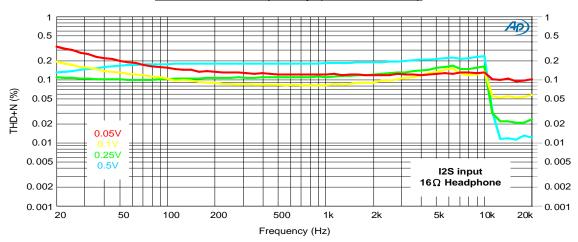

# **Electrical Characteristics and Specifications for Headphone**

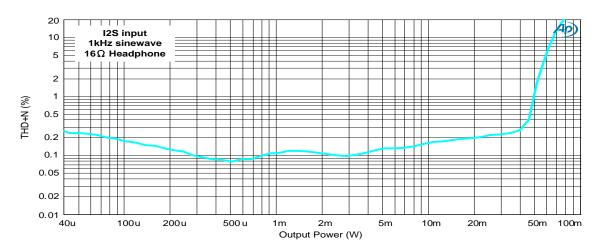

• Condition:  $T_A=25^{\circ}C$ ; VDD5=PVDD=AVDD2=5V; AVDD=3.3V;  $F_S=48$ kHz; I2S input; Load=16 $\Omega$ ; Input is 1kHz sinewave unless otherwise specified.

| Symbol | Parameter                           | Condition | Input Level          | Min | Тур  | Max | Units |

|--------|-------------------------------------|-----------|----------------------|-----|------|-----|-------|

| В      | RMS Output Power for Each Channel   | THD+N=10% |                      |     | 66   |     | mW    |

| Po     | Kivis Output Fower for Each Charmer | THD+N=1%  |                      |     | 49   |     | mW    |

| THD+N  | Total Harmonic Distortion + Noise   | 10mW      |                      |     | 0.17 |     | %     |

| I HD+N | Total Harmonic Distortion + Noise   | 1mW       |                      |     | 0.11 |     | %     |

| SNR    | Signal to Noise Ratio (Note 1)      |           | -1dB                 |     | 89   |     | dB    |

| DR     | Dynamic Range (Note 1)              |           | -60dB                |     | 91   |     | dB    |

|        | Channel Separation                  | @1kHz     | P <sub>O</sub> =0.5V |     | 84   |     | dB    |

|        | Noise level                         |           |                      |     | 46   |     | uV    |

Note 1: Measured with A-weighting filter and external power.

# THD+N vs. Frequency (Load: 16ohm)

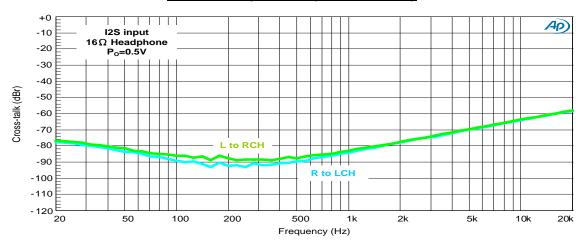

## Channel Separation (Load: 16ohm)

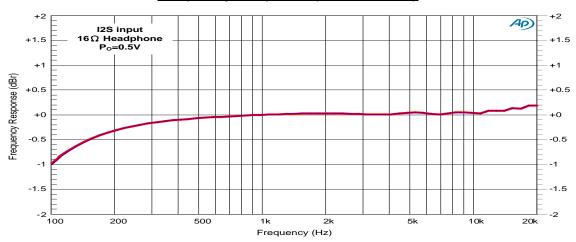

#### Frequency Response (Load: 16ohm)

Publication Date: Aug. 2021

Revision: 1.1

9/34

# **Electrical Characteristics and Specifications for Headphone**

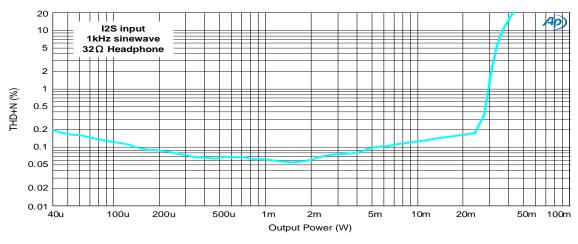

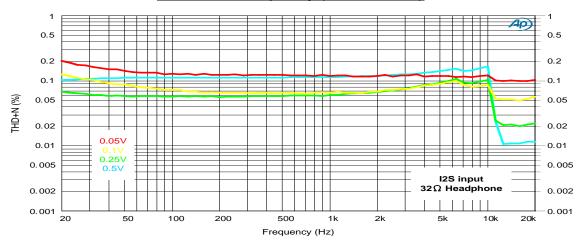

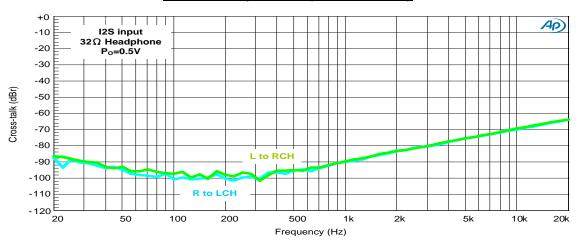

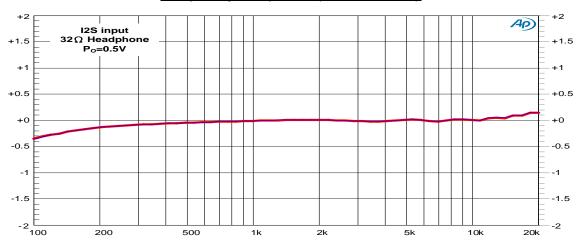

• Condition:  $T_A=25^{\circ}C$ ; VDD5=PVDD=AVDD2=5V; AVDD=3.3V;  $F_S=48$ kHz; I2S input; Load=32 $\Omega$ ; Input is 1kHz sinewave unless otherwise specified.

| Symbol | Parameter                           | Condition | Input Level          | Min | Тур  | Max | Units |

|--------|-------------------------------------|-----------|----------------------|-----|------|-----|-------|

| В      | RMS Output Power for Each Channel   | THD+N=10% |                      |     | 37   |     | mW    |

| Po     | Kivis Output Fower for Each Charmer | THD+N=1%  |                      |     | 29   |     | mW    |

| THD+N  | Total Harmonic Distortion + Noise   | 10mW      |                      |     | 0.13 |     | %     |

| I HD+N | Total Harmonic Distortion + Noise   | 1mW       |                      |     | 0.06 |     | %     |

| SNR    | Signal to Noise Ratio (Note 2)      |           | -1dB                 |     | 91   |     | dB    |

| DR     | Dynamic Range (Note 2)              |           | -60dB                |     | 91   |     | dB    |

|        | Channel Separation                  | @1kHz     | P <sub>O</sub> =0.5V |     | 89   |     | dB    |

|        | Noise level                         |           |                      |     | 45   |     | uV    |

Note 2: Measured with A-weighting filter and external power.

Publication Date: Aug. 2021 Revision: 1.1 10/34

# THD+N vs. Frequency (Load: 32ohm)

## Channel Separation (Load: 32ohm)

#### Frequency Response (Load: 32ohm)

Publication Date: Aug. 2021 Revision: 1.1 11/34

# **Interface Configuration**

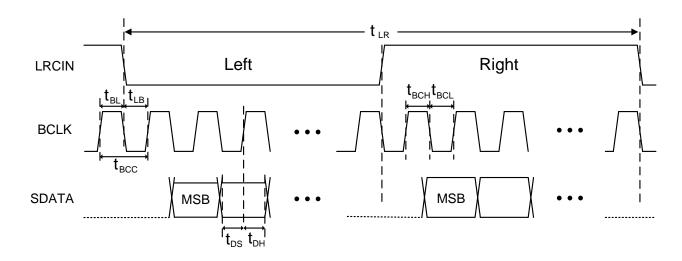

# I<sup>2</sup>S

| Symbol           | Parameter                         | Min    | Тур | Max   | Units |

|------------------|-----------------------------------|--------|-----|-------|-------|

| $t_{LR}$         | LRCIN Period (1/F <sub>S</sub> )  | 10.41  |     | 125   | μS    |

| t <sub>BL</sub>  | BCLK Rising Edge to LRCIN Edge    | 50     |     |       | ns    |

| t <sub>LB</sub>  | LRCIN Edge to BCLK Rising Edge    | 50     |     |       | ns    |

| t <sub>BCC</sub> | BCLK Period (1/64F <sub>S</sub> ) | 162.76 |     | 1953  | ns    |

| t <sub>BCH</sub> | BCLK Pulse Width High             | 81.38  |     | 976.5 | ns    |

| t <sub>BCL</sub> | BCLK Pulse Width Low              | 81.38  |     | 976.5 | ns    |

| t <sub>DS</sub>  | SDATA Set-Up Time                 | 50     |     |       | ns    |

| t <sub>DH</sub>  | SDATA Hold Time                   | 50     |     |       | ns    |

Publication Date: Aug. 2021 Revision: 1.1 12/34

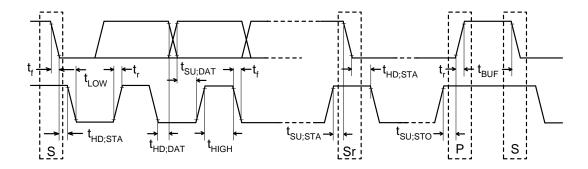

# • I<sup>2</sup>C Timing

| Doromotor                                       | Cymahal             | Standard   | Mode | Mode Fast Mod        |      | Llait |

|-------------------------------------------------|---------------------|------------|------|----------------------|------|-------|

| Parameter                                       | Symbol              | MIN.       | MAX. | MIN.                 | MAX. | Unit  |

| SCL clock frequency                             | f <sub>SCL</sub>    | 0          | 100  | 0                    | 400  | kHz   |

| Hold time (repeated) START condition            | t <sub>HD,STA</sub> | 4.0        |      | 0.6                  |      | μS    |

| LOW period of the SCL clock                     | t <sub>LOW</sub>    | 4.7        |      | 1.3                  |      | μS    |

| HIGH period of the SCL clock                    | t <sub>HIGH</sub>   | 4.0        |      | 0.6                  |      | μS    |

| Setup time for a repeated START condition       | t <sub>SU;STA</sub> | 4.7        |      | 0.6                  |      | μS    |

| Data hold time for I <sup>2</sup> C bus devices | t <sub>HD;DAT</sub> | 0          | 3.45 | 0                    | 0.9  | μS    |

| Data setup time                                 | t <sub>SU;DAT</sub> | 250        |      | 100                  |      | ns    |

| Rise time of both SDA and SCL signals           | t <sub>r</sub>      |            | 1000 | 20+0.1Cb             | 300  | ns    |

| Fall time of both SDA and SCL signals           | t <sub>f</sub>      |            | 300  | 20+0.1Cb             | 300  | ns    |

| Setup time for STOP condition                   | t <sub>SU;STO</sub> | 4.0        |      | 0.6                  |      | μS    |

| Bus free time between a STOP and START          | <b>t</b>            | 4.7        |      | 1.3                  |      | 0     |

| condition                                       | t <sub>BUF</sub>    | 4.7        |      | 1.3                  |      | μS    |

| Capacitive load for each bus line               | C <sub>b</sub>      |            | 400  |                      | 400  | pF    |

| Noise margin at the LOW level for each          | W                   | 0.1        |      | 0.1V <sub>REGO</sub> |      | V     |

| connected device (including hysteresis)         | $V_{nL}$            | $V_{REGO}$ |      | U. I V REGO          |      | V     |

| Noise margin at the HIGH level for each         | V                   | 0.2        |      | 0.21/                |      | V     |

| connected device (including hysteresis)         | $V_{nH}$            | $V_{REGO}$ |      | 0.2V <sub>REGO</sub> |      | V     |

Publication Date: Aug. 2021 Revision: 1.1 13/34

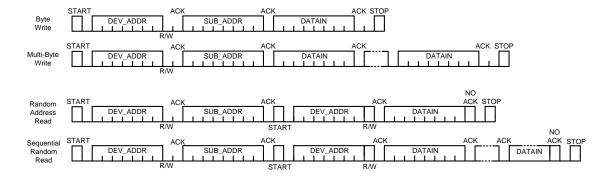

# **I<sup>2</sup>C-Bus Transfer Protocol**

#### Introduction

AD62556 employs I<sup>2</sup>C-bus transfer protocol. Two wires, serial data (SDA) and serial clock (SCL), carry information between the devices connected to the bus. Each device is recognized by a unique 7-bit address and can operate as either a transmitter or a receiver. The master device initiates a data transfer and provides the serial clock (SCL) on the bus. AD62556 is also a slave device in all of its communications.

#### Protocol

#### START and STOP condition

START is identified by a high to low transition of the data bus SDA signal while the clock signal SCL is stable in the high state. A START condition must be preceding any command for data transfer. A low to high transition on the SDA line while SCL is high defines a STOP condition. A STOP condition terminates communication between AD62556 and the master device on the bus.

#### Data validity

The data on the SDA line must be stable during the high period of the clock. The high or low state of the data line can only change when the clock signal on the SCL line is low. AD62556 samples the SDA signal at rising edge of the clock signal SCL.

#### Device addressing

The master generates 7-bit address to recognize slave device. When AD62556 receives 7-bit address matched with 7'b0111010, AD62556 will acknowledge at 9th bit time (8th bit time is for R/W bit). The bytes following the device identification address are interpreted as internal sub-addresses.

#### Data transferring

Every byte put on SDA line must be 8-bits long. Each byte has to be followed by an acknowledge bit. Data is transferred with MSB first. As the figure shown below, in both write and read operation, AD62556 supports single-byte and multi-byte. Please refer to the figure shown below for detail data-transferring protocol.

Publication Date: Aug. 2021 Revision: 1.1 14/34

#### **Operation Descriptions**

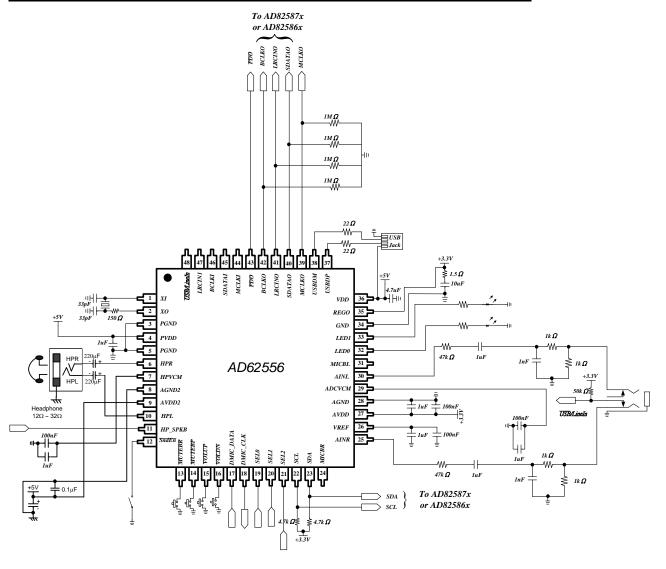

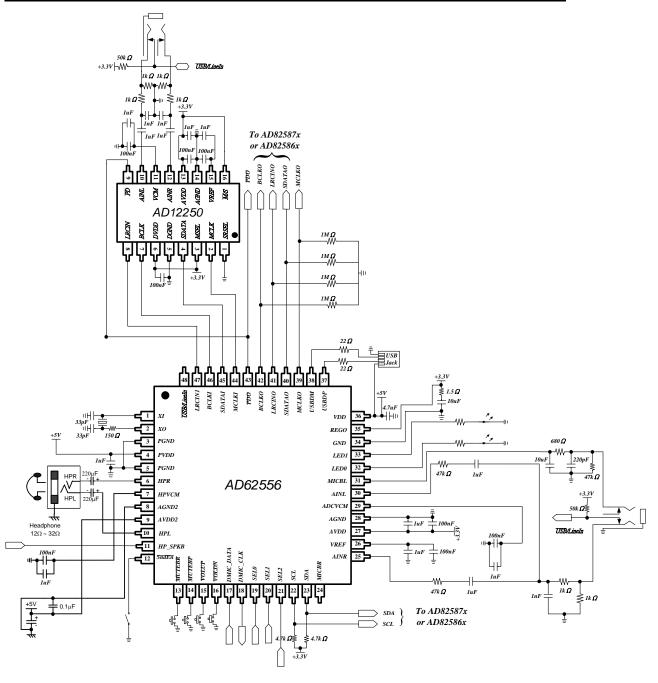

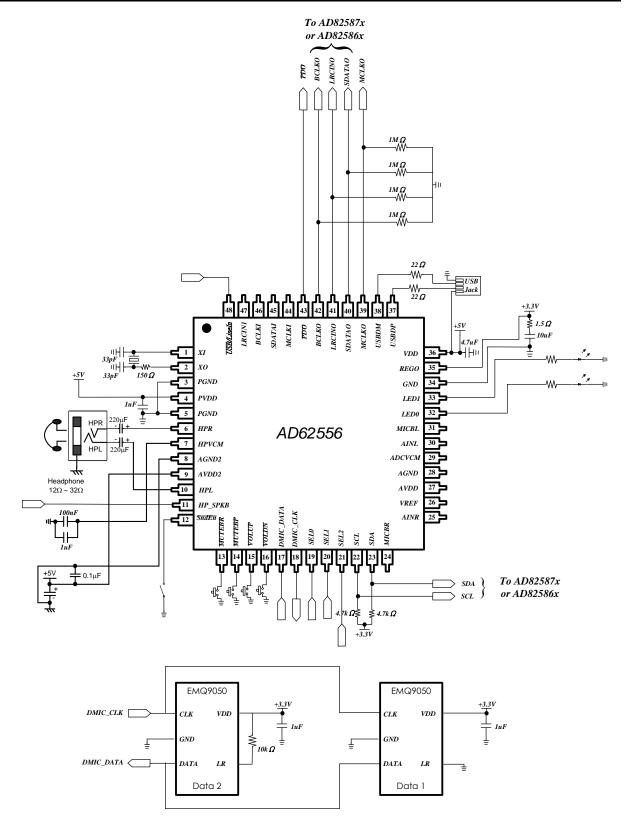

The following figure illustrates two more advanced applications that use AD62556, together with an internal ADC or an external ADC, e.g., AD12250 from ESMT that can convert stereo line-in audio to I<sup>2</sup>S output to send to AD62556, and/or an external high-end class D amplifier such as AD82586x/AD82587x.

Both applications, a switch used to select audio stream from either USB port or Line-in port. When the audio stream is from Line-in port, the device is operating as "docking station" mode. When the audio stream is from USB port, the device is operating as "USB headphone" mode. When AD82586x/AD82587x is used, since it can deliver 10Wx2 + 20W (subwoofer) power or 20Wx2 power, USB bus power may be insufficient and local power supply is required. Functional description follows.

#### SEL2, SEL1, SEL0

|      | 0       | 1                |

|------|---------|------------------|

| SEL0 | AD8287x | AD82586x/AD83586 |

| SEL2 | SEL1 | Audio Source                           |  |

|------|------|----------------------------------------|--|

| 0    | 0    | Internal ADC as line-in                |  |

| 1    | 0    | Internal ADC as Microphone             |  |

| 0    | 1    | External ADC as line-in, such AD12250  |  |

| 1    | 1    | Digital Microphone input, such EMQ9050 |  |

#### **RESET**

The AD62556 has embedded power on reset circuit. When AD62556 power on, need wait 0.5ms reset process for the system ready.

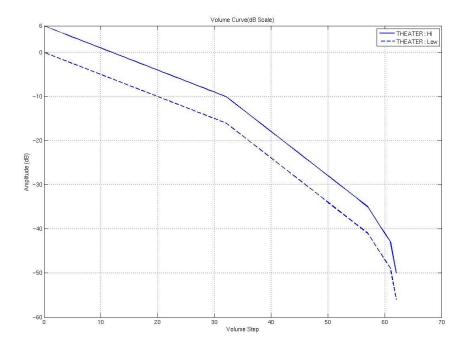

#### **Volume Control of Playback**

Audio volume control up/down is low active by VOLUPB/VOLDNB pins. VOLUPB and VOLDNB also support the USB HID device class for host panel control synchronization. Duration of low level must be longer than 3ms. The default volume gain is +6dB referred to the original input signal level.

Publication Date: Aug. 2021 Revision: 1.1 15/34

The volume gain range is from +6 dB to -50 dB.

#### **Volume Control of Recording**

The volume gain range is from +6 dB to -50 dB the same as the playback.

#### **Mute control**

Both MUTEB and MUTEBR are low active. Only MUTEB supports USB HID device class for host panel control synchronization. Duration of low level must be longer than 3ms.

#### Stereo dual ADC

AD62556 has a dual channel stereo ADC input as microphone or line-in recording source according to SEL1 and SEL2 pins. After USB plug in, the USB descriptor can be changed accordingly.

#### **LED display**

LED0 can be used as USB operation indicator when data transmit. LED1 can be used as recording mute indicator, it can be controlled by OS and MUTEBR.

#### **Microphone Gain Boost**

When use internal ADC as microphone in the AD62556, the internal gain boost has two stages. One is 20dB and the other can select from 0dB to 22.5dB.

Publication Date: Aug. 2021 Revision: 1.1 16/34

#### **Self-protection circuit**

AD62556 has built-in thermal, short-circuit and under-voltage detection circuits. If the internal thermal detection junction temperature is higher than 150°C, the output will be turned off. The thermal detection circuit has a temperature hysteretic characteristic such that the AD62556 will return to normal operation when the device is cooled down to about 30°C. Due to the process variation, the triggering temperature values can have around 10% variation.

To protect headphone power driver when the headphone output are shorted each other or shorted to VDD or GND, the output loading detection circuits are built-in and proper protection action will take place once the short circuit condition is detected.

#### Anti-pop design

AD62556 is has an anti-pop circuit to suppress the annoying pop sounds during initial power on, power down/up, mute, power off and volume level change.

#### **Under Voltage protection circuit**

Once the  $V_{DD5}$  is lower than 3.7V, AD62556 will turn off its headphone driver and the digital circuit will cease operation. When  $V_{DD5}$  becomes larger than 3.8V, AD62556 will return to normal operation.

#### Switching between USB mode and docking station mode

When the USB/LineIn pin is low, the input audio stream is from USB port as USB headphone mode. When this pin is high, the input audio stream is from AINL/AINR, I<sup>2</sup>S input port or DMIC\_DATAL/DMIC\_DATAR as docking station mode.

#### Audio Recording

AD62556 can record external audio source from AINL/AINR microphone/line in, I<sup>2</sup>S SDATAI or DMIC\_DATAL/DMIC\_DATAR digital microphone by SEL1 and SEL2 pins. Supports 44.1kHz and 48kHz sampling frequency for audio recording, the default setting is 48kHz for audio recording in AD62556.

#### 3D Surround sound Mode

When SndEn pin is low, 3D surround sound Mode is enabled. AD62556 provides the virtual surround sound technology with greater separation and depth for stereo signals and synthesizes a 3D stereo sound field.

#### **Power Consideration**

AD62556 can be powered by the USB port directly. However, the maximum current supplied by each USB port is limited 500mA. If the total power requirement of the USB audio subsystem is higher than this, local power supply, e.g., a local AC adaptor will have to be used. If the audio subsystem is attached to an USB hub, which is not locally powered, the maximum power from each USB port is only limited to 100mA, and local power must be supplied.

#### **Power Clipping**

AD62556 support power clipping function for protect speaker. There are 16 levels can be set through I2C.

#### I<sup>2</sup>C master/slave mode

AD62556 can also operate as master or slave in a system when LRCINO is pulled low or high with  $1M\Omega$  at power up initially (during 15ms after 90% of  $V_{REGO}$ ). When LRCINO is pulled low, the AD62556 operates as I2C master mode. In I2C master mode, the AD62556 also can control the external class-D amp. AD82586/AD82581 via I2C. When LRCINO is pulled high, the AD62556 operates as I2C slave mode. When operating as a slave mode, AD62556's functions are controlled by micro-controller. Functions in PC are all disable.

#### I<sup>2</sup>S master/slave mode

The pins LRCINI, BCLKI and MCLKI of the AD62556 can also operate as I2S master or slave mode in a system when BCLKO is pulled low or high with  $1M\Omega$ at power up initially (during 15ms after 90% of  $V_{REGO}$ ). When BCLKO is pulled low, the AD62556 operates as I2S master mode. In I2S master mode, the pins LRCINI, BCLKI and MCLKI are output pins can drive the other devices. When BCLKO is pulled high, the AD62556 operates as I2S slave mode. When operating as a slave mode, the pins LRCINI, BCLKI and MCLKI are input pins need the other device provide clocks.

Note 1: In slave mode, it must be followed the frequency ratio of MCLKI = 256×LRCINI for correct operation.

Note 2: In slave mode, AD62556 only support I2S source playback and can't support USB source playback/recording.

Publication Date: Aug. 2021 Revision: 1.1 18/34

#### Mixing mode

The AD62556 can mix USB audio signal and anlog/I2S audio signal to the output when MCLKO is pulled high with  $1M\Omega$  at power up initially (during 15ms after 90% of  $V_{REGO}$ ). When MCLKO is pulled high, the volume of mixing signal can control through address 8 and 9 via I2C. Also can mute and un-mute mixing signal through the bit 5 and 6 of the address 1.

#### Stereo/Mono mode

The output of the AD62556 can configure the stereo or mono mode when SDATAO is pulled high or low with  $1M\Omega$  at power up initially (during 15ms after 90% of  $V_{REGO}$ ). When SDATAO is pulled low, the output of the AD62556 is the stereo mode. When SDATAO is pulled high, the output of the AD62556 is the mono mode and the audio signal is mix from the left and right channel.

#### Switching between headphone mode and I2S output mode

When the HP\_SPK pin is low, it is I2S output mode and the audio output is from SDATAO. When this pin is high, it turns to headphone mode and the output is only from pins HPL and HPR.

#### **Register Table**

The audio signal processing data flow is shown as the following figure. Users can control these functions by programming appropriate setting to register table, which is summarized in this section. More detail information will be described in next section.

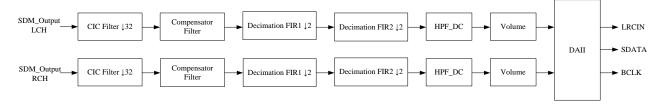

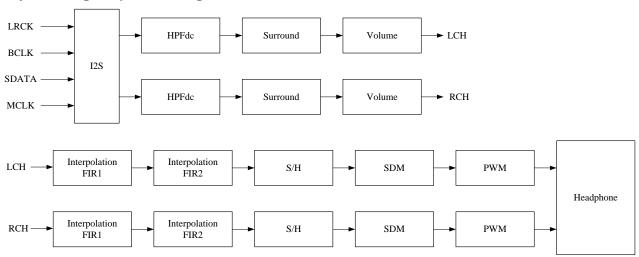

## Recording signal processing flow

## Playback signal processing flow

| Add. | Name    | B[7]        | B[6]         | B[5]          | B[4]          | B[3]          | B[2]          | B[1]          | B[0]          |

|------|---------|-------------|--------------|---------------|---------------|---------------|---------------|---------------|---------------|

| 0X00 | PB_CTL  | Reserved    | MIX_CH1_MUTE | MIX_CH2_MUTE  | PB_ZDEN       | PB_SRSEN      | PB_HPF        | PB_CH1_MUTE   | PB_CH2_MUTE   |

| 0X01 | PB_LVOL | Rese        | erved        | PB_CH1Vol [5] | PB_CH1Vol [4] | PB_CH1Vol [3] | PB_CH1Vol [2] | PB_CH1Vol [1] | PB_CH1Vol [0] |

| 0X02 | PB_RVOL | Rese        | erved        | PB_CH2Vol [5] | PB_CH2Vol [4] | PB_CH2Vol [3] | PB_CH2Vol [2] | PB_CH2Vol [1] | PB_CH2Vol [0] |

| 0X03 | RE_CTL  | ADC_V3      | ADC_V2       | ADC_V1        | ADC_V0        | ADC_BOOST     | RE_HPF        | RE_CH1_Mute   | RE_CH2_Mute   |

| 0X04 | RE_LVOL | C1V[7]      | C1V[6]       | RE_CH1Vol [5] | RE_CH1Vol [4] | RE_CH1Vol [3] | RE_CH1Vol [2] | RE_CH1Vol [1] | RE_CH1Vol [0] |

| 0X05 | RE_RVOL | C2V[7]      | C2V[6]       | RE_CH2Vol [5] | RE_CH2Vol [4] | RE_CH2Vol [3] | RE_CH2Vol [2] | RE_CH2Vol [1] | RE_CH2Vol [0] |

| 0X06 | ZD&MICB | ZD_LEVEL[1] | ZD_LEVEL[0]  | Reserved      |               | MICBPDB       | MBVSEL[1]     | MBVSEL[0]     |               |

| 0X07 | PL      |             | Reserved     |               | PL_EN         | PL_Level [3]  | PL_Level [2]  | PL_Level [1]  | PL_Level [0]  |

Publication Date: Aug. 2021

Revision: 1.1 20/34

# **Detail Description for Register**

In this section, please note that the highlighted columns are the default value of these tables. If no highlighted, it is because the default setting of this bit is determined by external pin.

Address 0: Playback State control

| BIT  | NAME          | DESCRIPTION                       | VALUE | FUNCTION |

|------|---------------|-----------------------------------|-------|----------|

| B[7] | Reserved      |                                   |       |          |

| B[6] | MIX_CH1_MUTE  | Mixing Channel1 Mute              | 1     | Mute     |

| D[0] | WIX_CITI_WOTE | wixing Charmer wide               | 0     | Un-mute  |

| DIEI | MIV CHO MUTE  | Mining Changel Muta               | 1     | Mute     |

| B[5] | MIX_CH2_MUTE  | Mixing Channel2 Mute              | 0     | Un-mute  |

| DIAI | DD ZDENI      | Playback Zero-Detection<br>Enable | 1     | Enable   |

| B[4] | PB_ZDEN       |                                   | 0     | Disable  |

| DIOI | DD CDCEN      | Playback Surround Enable          | 1     | Enable   |

| B[3] | PB_SRSEN      |                                   | 0     | Disable  |

| DIO  | DD LIDE       | Dlaybook High Doog Filter         | 1     | Enable   |

| B[2] | PB_HPF        | Playback High Pass Filter         | 0     | Disable  |

| DIAI | DD CHA MUTE   | Dischards Observed Mate           | 1     | Mute     |

| B[1] | PB_CH1_MUTE   | Playback Channel1 Mute            | 0     | Un-mute  |

| DIOI | DD CHO MUTE   | Playbook Channel Musta            | 1     | Mute     |

| B[0] | PB_CH2_MUTE   | Playback Channel2 Mute            | 0     | Un-mute  |

Publication Date: Aug. 2021 Revision: 1.1 21/34

Address 1: Playback Left Channel Volume Control

| BIT    | NAME                  | DESCRIPTION                 | Value  | FUNCTION |

|--------|-----------------------|-----------------------------|--------|----------|

|        |                       |                             | 000000 | +6dB     |

|        |                       |                             | 000001 | +5.5dB   |

|        |                       | Dlovbook                    |        |          |

|        | B[5:0] PB_CH1Vol[5:0] | Playback                    | 001100 | +0dB     |

| DIE-OI |                       | Left Channel Volume Control | 001101 | -0.5dB   |

| D[3.0] |                       |                             |        |          |

|        |                       |                             | 100000 | -10dB    |

|        |                       |                             | 100001 | -11dB    |

|        |                       |                             |        |          |

|        |                       |                             | 111111 | -∞dB     |

# Address 2: Playback Right Channel Volume Control

| BIT    | NAME                  | DESCRIPTION                  | Value  | FUNCTION |

|--------|-----------------------|------------------------------|--------|----------|

|        |                       |                              | 000000 | +6dB     |

|        |                       |                              | 000001 | +5.5dB   |

|        |                       | Dlavkask                     |        |          |

|        | B[5:0] PB_CH2Vol[5:0] | Playback                     | 001100 | +0dB     |

| DIE:01 |                       | Right Channel Volume Control | 001101 | -0.5dB   |

| D[3.0] |                       |                              |        |          |

|        |                       |                              | 100000 | -10dB    |

|        |                       |                              | 100001 | -11dB    |

|        |                       |                              |        |          |

|        |                       |                              | 111111 | -∞dB     |

Publication Date: Aug. 2021 Revision: 1.1 22/34

Address 3: Recording State control

| BIT              | NAME                                         | DESCRIPTION                          | VALUE | FUNCTION |

|------------------|----------------------------------------------|--------------------------------------|-------|----------|

|                  |                                              |                                      | 0000  | 0 dB     |

| רבז              | ADC_V3                                       |                                      | 0001  | 5 dB     |

| B[7]             | ADC_V3                                       |                                      | 0010  | 8 dB     |

|                  |                                              |                                      | 0011  | 10 dB    |

|                  |                                              |                                      | 0100  | 12 dB    |

| B[6]             | ADC_V2                                       |                                      | 0101  | 14 dB    |

| ا ا              | ADO_V2                                       |                                      | 0110  | 15 dB    |

|                  |                                              | DESCRIPTION                          | 0111  | 16.6 dB  |

|                  | 2 <sup>nd</sup> OP Gain control  B[5] ADC_V1 | 2 <sup>nd</sup> OP Gain control      | 1000  | 17.6 dB  |

| RI51             |                                              |                                      | 1001  | 18.6 dB  |

| ال ال            |                                              | ADC_V1                               | 1010  | 19.2 dB  |

|                  |                                              |                                      | 1011  | 19.8 dB  |

|                  |                                              |                                      | 1100  | 20.4 dB  |

| B[4]             | ADC VO                                       |                                      | 1101  | 21 dB    |

| D[4]             | ADO_V0                                       |                                      | 1110  | 21.7 dB  |

|                  |                                              |                                      | 1111  | 22.5 dB  |

| B[3]             | ADC_BOOST                                    | 1 <sup>st</sup> OP Gain boost enable | 1     | Enable   |

| ارق]             | AD0_B0001                                    | 1 Of Gaill boost enable              | 0     | Disable  |

| B[2]             | RE_HPF                                       | Recording High Pass Filter           | 1     | Enable   |

| ارک <sub>ا</sub> | IXE_FIFT                                     | Recording Fight Pass Filter          | 0     | Disable  |

| B[1]             | RE_CH1_Mute                                  | Recording Channel Muta               | 1     | Mute     |

| וויןט            | NE_OFFI_Widte                                | Recording Channel1 Mute              | 0     | Un-mute  |

| B[0]             | RF CH2 Mute                                  | Recording Channel2 Mute              | 1     | Mute     |

| P[O]             | RE_CH2_Mute                                  | 1.000rding Orianneiz Mute            | 0     | Un-mute  |

Publication Date: Aug. 2021 Revision: 1.1 23/34

# **Address 4: Recording Left Channel Volume Control**

| BIT    | NAME           | DESCRIPTION                 | Value  | FUNCTION |

|--------|----------------|-----------------------------|--------|----------|

|        |                |                             | 000000 | +6dB     |

|        |                |                             | 000001 | +5.5dB   |

|        |                | Decording                   |        |          |

|        |                | Recording                   | 001100 | +0dB     |

| DIE:01 |                | Left Channel Volume Control | 001101 | -0.5dB   |

| B[5:0] | PB_CH1Vol[5:0] |                             |        |          |

|        |                |                             | 100000 | -10dB    |

|        |                |                             | 100001 | -11dB    |

|        |                |                             |        |          |

|        |                |                             | 111111 | -∞dB     |

# **Address 5: Recording Right Channel Volume Control**

| BIT    | NAME            | DESCRIPTION                                            | Value  | FUNCTION |

|--------|-----------------|--------------------------------------------------------|--------|----------|

|        |                 |                                                        | 000000 | +6dB     |

|        |                 |                                                        | 000001 | +5.5dB   |

|        |                 | Departing                                              |        |          |

|        |                 | Recording                                              | 001100 | +0dB     |

| DIE:01 | DD CH3\/al[E:0] | Right 001101  H2Vol[5:0] Channel  Volume 100000 100001 | 001101 | -0.5dB   |

| B[5:0] | PB_CH2V0[5:0]   |                                                        |        |          |

|        |                 |                                                        | -10dB  |          |

|        |                 |                                                        | 100001 | -11dB    |

|        |                 |                                                        |        |          |

|        |                 |                                                        | 111111 | -∞dB     |

Publication Date: Aug. 2021 Revision: 1.1 24/34

Address 6: Zero-Detection and Mic. Bias Setting

| BIT    | NAME     | DESCRIPTION             | VALUE | FUNCTION   |

|--------|----------|-------------------------|-------|------------|

|        |          |                         | 11    | -60dB      |

| DIZ.Cl | 7D   EVE | Zara Datastian Laval    | 10    | -70dB      |

| B[7:6] | ZD_LEVEL | Zero Detection Level    | 01    | -80dB      |

|        |          |                         | 00    | zero       |

| B[5]   | Reserved |                         |       |            |

| B[4]   | Reserved |                         |       |            |

| B[3]   | Reserved |                         |       |            |

| D[O]   | MICBPDB  | Microphone Bias Voltage | 0     | Power down |

| B[2]   | MICEPDE  | PowerDown               | 1     | Power up   |

|        |          |                         | 11    | 0.9*AVDD   |

| B[1:0] | MBVSEL   | Microphone Bias Voltage | 10    | 0.8*AVDD   |

| B[1:0] | IVIDVOEL | Control                 | 01    | 0.6*AVDD   |

|        |          |                         | 00    | 0.5*AVDD   |

Publication Date: Aug. 2021 Revision: 1.1 25/34

# **Address 7: Power Clipping Setting**

| BIT  | NAME     | DESCRIPTION           | VALUE | FUNCTION |

|------|----------|-----------------------|-------|----------|

| B[7] | Reserved |                       |       |          |

| B[6] | Reserved |                       |       |          |

| B[5] | Reserved |                       |       |          |

| DIAI | DC EN    | Dower Clipping Engblo | 1     | Enable   |

| B[4] | PC_EN    | Power Clipping Enable | 0     | Disable  |

| B[3] | Diol     |                       | 0000  | 0dB      |

| D[0] |          |                       | 0001  | -2dB     |

| וכום |          |                       | 0010  | -4 dB    |

| B[2] | PC_Level |                       | 0011  | -6dB     |

| D[1] | FO_Level | Power Clipping Level  | 0100  | -8 dB    |

| D[1] | B[1]     |                       |       |          |

| BIOI |          |                       | 1110  | -28 dB   |

| B[0] |          |                       | 1111  | -30 dB   |

Publication Date: Aug. 2021 Revision: 1.1 26/34

# **Address 8: Mixing Left Channel Volume Control**

| BIT    | NAME            | DESCRIPTION | Value  | FUNCTION |

|--------|-----------------|-------------|--------|----------|

| B[5:0] | Mix_CH1Vol[5:0] | Mixing      | 000000 | +6dB     |

|        |                 | Left        | 000001 | +5.5dB   |

|        |                 | Channel     |        |          |

|        |                 | Volume      | 001100 | +0dB     |

|        |                 | Control     | 001101 | -0.5dB   |

|        |                 |             |        |          |

|        |                 |             | 100000 | -10dB    |

|        |                 |             | 100001 | -11dB    |

|        |                 |             |        |          |

|        |                 |             | 111111 | -∞dB     |

## **Address 9: Mixing Right Channel Volume Control**

| BIT    | NAME            | DESCRIPTION | Value  | FUNCTION |

|--------|-----------------|-------------|--------|----------|

| B[5:0] | Mix_CH2Vol[5:0] | Mixing      | 000000 | +6dB     |

|        |                 | Right       | 000001 | +5.5dB   |

|        |                 | Channel     |        |          |

|        |                 | Volume      | 001100 | +0dB     |

|        |                 | Control     | 001101 | -0.5dB   |

|        |                 |             |        |          |

|        |                 |             | 100000 | -10dB    |

|        |                 |             | 100001 | -11dB    |

|        |                 |             |        |          |

|        |                 |             | 111111 | -∞dB     |

Publication Date: Aug. 2021

Revision: 1.1

#### Application Circuit Examples for Headphone, External ADC as Line-in 50k Ω +3.3V USB/LineIn 1kΩ 1kΩ ₩<del>•</del>₩ To AD82587x or AD82586x AD12250 +3.3V 22 Ω ₩-₹ 1.5Ω SDATAI LRCINO BCLKIMCLKI BCLKOUSBDM SDATAO USBDP DDOVDD хo REGO PGND GNDPVDD LED1 PGND LED0 HPR MICBL AD62556 HPVCM AINLADCVCM AGND AVDD2 Headphone AVDD 12Ω ~ 32Ω VREF **4**11 HP\_SPKB AINR 12 SELI To AD82587x SDA ) . 4<sup>2</sup> 4<sup>2</sup> or AD82586x

Publication Date: Aug. 2021 Revision: 1.1 **28/34**

# Application Circuit Examples for Headphone, Internal ADC as Line-in

Publication Date: Aug. 2021

Revision: 1.1

29/34

# Application Circuit Examples for Headphone, Internal ADC as Microphone

Publication Date: Aug. 2021 Revision: 1.1 **30/34**

# Application Circuit Examples for Headphone with Digital Microphone Module input

Publication Date: Aug. 2021 Revision: 1.1 31/34

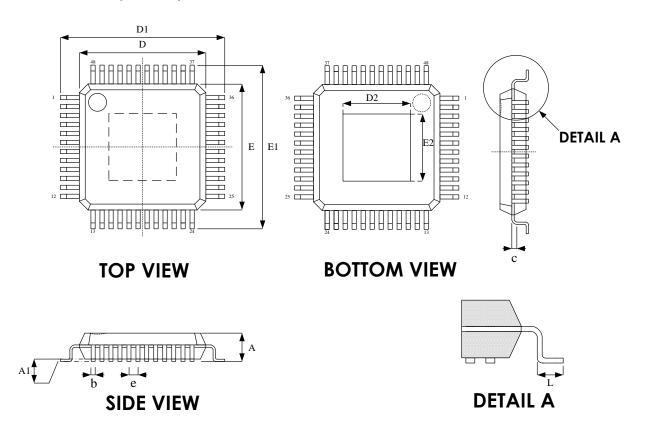

# **Package Dimensions**

# • E-LQFP 48L (7x7mm)

| Crussle of | Dimension in mm |      |  |

|------------|-----------------|------|--|

| Symbol     | Min             | Max  |  |

| А          |                 | 1.60 |  |

| A1         | 0.05            | 0.15 |  |

| Ъ          | 0.17            | 0.27 |  |

| С          | 0.09            | 0.20 |  |

| D          | 6.90            | 7.10 |  |

| D1         | 8.90            | 9.10 |  |

| Е          | 6.90            | 7.10 |  |

| E1         | 8.90            | 9.10 |  |

| е          | 0.50 BSC        |      |  |

| L          | 0.45            | 0.75 |  |

| Exposed pad |                 |      |  |

|-------------|-----------------|------|--|

|             | Dimension in mm |      |  |

|             | Min             | Max  |  |

| D2          | 4.31            | 5.21 |  |

| E2          | 4.31            | 5.21 |  |

Publication Date: Aug. 2021

Revision: 1.1 32/34

# **Revision History**

| Revision | Date       | Description                                                                                                                                                                                                                                                                                                                               |  |

|----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0.1      | 2013.07.11 | Original version.                                                                                                                                                                                                                                                                                                                         |  |

| 0.2      | 2013.10.24 | 1) Corrected the pin of AVDD2 is 5V power pin, not 3.3V power pin. 2) Removed 5V tolerant I/O. 3) Put 3.3V regulator V <sub>REGO</sub> spec. into this datasheet. 4) Changed 3.3V regulator lout spec from 200mA to 100mA. 5) Removed EMP logo. 6) Updated I2C and I2S master/slave mode description, that's set during power on initial. |  |

| 0.3      | 2014.08.04 | <ol> <li>Add feature note about I2S Master/Slave mode.</li> <li>Modify Pin Description Table(SDA, SCL)</li> </ol>                                                                                                                                                                                                                         |  |

| 1.0      | 2015.02.17 | Remove preliminary word and modify version to 1.0                                                                                                                                                                                                                                                                                         |  |

| 1.1      | 2021.09.02 | <ol> <li>Update Volume Control of Playback.</li> <li>Update Mute Control.</li> <li>Update LED Display.</li> </ol>                                                                                                                                                                                                                         |  |

Publication Date: Aug. 2021

Revision: 1.1 33/34

# **Important Notice**

All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of ESMT.

The contents contained in this document are believed to be accurate at the time of publication. ESMT assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by ESMT for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of ESMT or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

ESMT's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.

Publication Date: Aug. 2021 Revision: 1.1 34/34